异构集成日趋成为半导体创新的关键,帮助提高半导体产品的价值、增加功能、维持及提高性能并能降低成本的先进封装技术。作为当前应用最为主流的先进封装技术之一,扇出型封装又分为扇出型晶圆级封装(Fan-Out Wafer Level Packaging;FOWLP),以及扇出型面板级封装(Fan-Out Panel Level Packaging;FOPLP)。两者虽工艺路线及应用不同,但皆可让最终产品达到更轻薄的外型。

厦门云天半导体科技有限公司董事长于大全指出,FOPLP技术的雏形是埋入基板式的封装,将一些无源器件或功率器件埋入在基板里面进行RDL互连,形成一个小型化的解决方案。随后业内发现相比FOWLP它的封装尺寸更大,成本更低,很快就成为封装领域的研发热点。

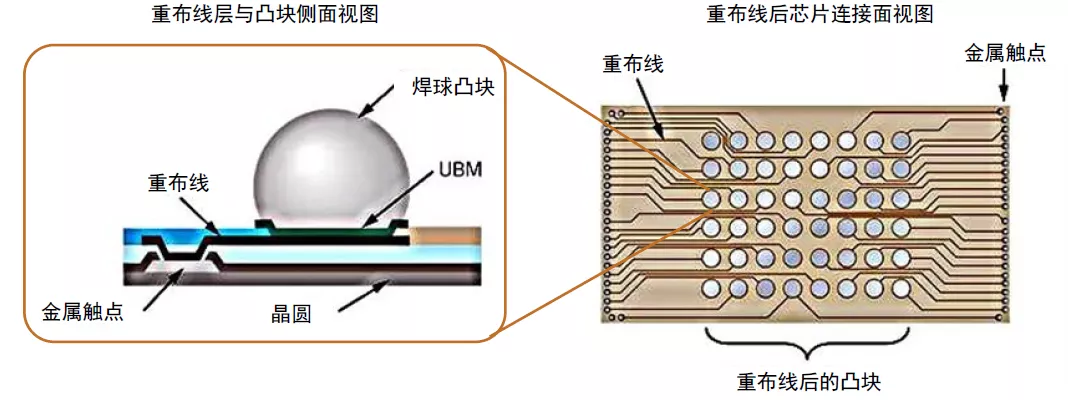

不过FOPLP仍面临非常多挑战,应用方面的主要挑战是目前适用该技术的产品类型还不够丰富,比较单一;装备、工艺方面的主要挑战包括曝光、显影、精密布线等制程,以及Die-to-Wafer的转移精度、效率、速度等面临一系列的挑战。此外,无论是FOWLP还是FOPLP,扇出型封装中异质整合了各类尺寸极小但功能强大的芯片,如何将他们合理布置到PCB上并实现高效的电气连接成为有效运转的系统,如何形成高膜厚均匀性且高分辨率的RDL(Redistribution layer,重布线层)技术成为关键的技术挑战之一。

RDL成为扇出型封装中异质整合的重要挑战

RDL采用线宽和间距(line/space;L/S,也称为特诊尺寸,CD)来度量,线宽和间距分别是指金属布线的宽度和它们之间的距离,它实际上是在原本的晶圆上又加了一层或几层,先在衬底上沉积一层铜种子层,再在该结构上涂布一层光刻胶,然后利用光刻设备将其图案化。最后,电镀系统将铜金属化层沉积其中,形成最终的RDL。随着工艺技术的发展,通过RDL形成的金属布线的CD也会越来越小,从而提供更高的互连密度。

资料来源:《SiP与先进封装技术》,中金公司研究部

高精密设备制造商Manz亚智科技认为,大板级RDL工艺提供具有成本效益及较大面积的制造方式。以同样的方式制造,RDL工艺概念适用于精细特色的microLED和无源器件制造,相比FOWLP(300mm晶圆,芯片尺寸8mm×8mm)可降低66%的成本。不过挑战在于,随着FOPLP基板尺寸增加,大面积工艺均匀性和用于RDL生产的载体处理方法成为关键,包括基板变大带来的重量增加,材质多样化和翘曲;特定的基板尺寸维持工艺过程中产生低变异性及线路图案维度均匀性;电镀厚度均匀性等问题。

能够提供均匀的表面线路而不需要额外后处理的镀铜工艺是成功实现FOPLP封装的RDL镀层的关键。

除了上述技术挑战,RDL对相关半导体设备也提出了新的需求。该技术生产过程涉及括光刻机、刻蚀机、溅射台和CVD、电镀设备等。在FOPLP技术尚未形成完善的行业标准前,仍需要封装厂、设计公司、以及设备和材料公司一起通力协作,在制程、电镀化学以及制造设备等方面实现全面创新,以解决与特征内(Within-feature, WiF)均匀度、共面性、缺陷、可靠度和生产量的相关问题。

Manz亚智科技强调,设备商与材料商维持密切合作,解决客户结构性设计以及工艺集成的问题,能建立工艺的标准流程,导入自动化及生产监控。加上RDL整线与上下游设备线也需要再集成,以Manz亚智科技对于设备、工艺流程以及自动化软件及硬件集成的丰富经验,对于优化产线设计有着很大的帮助,同时能协助客户提高产量及良率,进而能够为终端消费者提供更高效能、更高性价比终端产品的FOPLP工艺走向前台。

下一代RDL应用面临新的电镀和集成挑战

扇出型封装使用RDL技术将不同芯片连接在一起,是非常重要的互连技术。于大全解释,扇出型技术主要可以分为三种类型:芯片先装/面朝下(chip-first/face-down)、芯片先装/面朝上(chip-first/face-up)和芯片后装(chip-last,有时候也称为RDL first)。前面两种chip first需要在扇出表面做精细布线,RDL first则需要在圆片和面板(载具)上线做精细布线,布线能力会更高。他认为,未来面板级封装若走向RDL first,需要的RDL是非常精密的,技术挑战也更高。

在低密度扇出型封装中,主要是CD大于8μm的(8-8μm)的RDL,高密度扇出型封装则有多层RDL,CD在8-8μm及以下。具有较小CD的重布线层能够减少扇出型封装中的重布线层数。这能降低整体封装成本并提高良率,因此RDL的CD取决于应用,在可预见的未来,5-5µm及以上的封装仍将是主流技术。在高端领域,日月光正朝着1-1μm及以下的RDL进军。与此同时,台积电也紧跟步伐,目前正在研发0.8μm和0.4μm的扇出型技术。

对于RDL的发展路线,于大全指出,先进封装中的异构集成需要通过RDL来进行个I/O的变换,如果未来RDL技术引入到2.5D/3D IC垂直方向的芯片堆叠中,也将成为非常重要的电气互连方案。而且从成本角度来看,RDL在FOWLP中的成本占比非常高,尤其是2,3层以上成本占比就非常高了。

当前主流的RDL仍在5-5μm及以上,当5G需求爬坡以及存储器带宽需求变高时,将推动市场对3-3μm和2-3μm及以下的更小CD的RDL需求。Yole报告指出,云基础设施、5G、自动驾 驶和人工智能革命将塑造未来十年的封装趋势,密度更高的多层RDL积层结构方法将成为有助于在系统层面满足“超越摩尔”要求的解决方案之一。

不论如何,随着RDL走向更细的互连线路、更多层数的立体堆叠,导线对于高机械强度、热稳定性与抗疲劳性等可靠性需求日趋严苛,不仅需要新的材料跟制程设备,也使得封装的生产良率、可靠度面临更严苛的挑战,需要材料、设备厂商推出新一代材料或制程设备机台,让业者得以将先进封装推向量产。Manz亚智科技将不断优化相关制程设备,以健全、高产能、具成本效益的解决方案,来助力客户实现不断演进的制程。FOPLP工艺走向前台。

(校对/holly)