1.Gartner:2025年全球半导体市场规模达7930亿美元,英伟达领跑,英特尔份额缩减至6%;

2.机构:2026年8英寸晶圆代工产能利用率增长,厂商涨价;

3.艾为推出高防护高带宽小型化Type-C接口保护新品;

4.台积电将大幅增加在美投资 再建至少五座芯片工厂;

1.Gartner:2025年全球半导体市场规模达7930亿美元,英伟达领跑,英特尔份额缩减至6%;

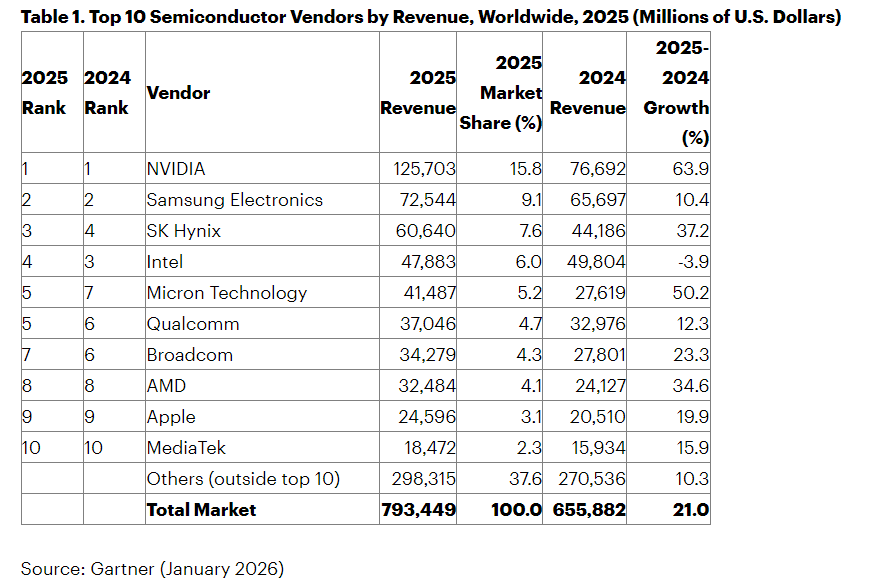

根据市场调查机构Gartner发布的初步统计数据,2025年全球半导体市场营收总额达7930亿美元,同比增长21%。

其中,人工智能(AI)相关半导体(包括处理器、高带宽内存HBM及网络组件)成为核心增长引擎,贡献了近三分之一的销售额,且预计到2026年AI基础设施支出将突破1.3万亿美元。

从厂商排名来看,在2025年全球十大半导体供应商排名中,五家企业位次较2024年发生变化。

英伟达以1257亿美元营收首次突破千亿美元大关,较2024年增长63.9%,市场份额达15.8%,领先第二名三星电子530亿美元,并贡献了行业超35%的增长。三星电子以725亿美元营收位列第二,其存储业务营收同比增长13%,但非存储业务下降8%。SK海力士凭借AI服务器对HBM的强劲需求,以606亿美元营收升至第三,同比增长37.2%。

英特尔市场份额从2021年的12%缩减至2025年的6%,营收同比下降3.9%至479亿美元,排名第四。美光科技以50.2%的增速(营收415亿美元)升至第五,高通(370亿美元,+12.3%)和博通(343亿美元,+23.3%)分列第六、七位。AMD营收增长34.6%至325亿美元,位列第八;苹果(246亿美元,+19.9%)和联发科(185亿美元,+15.9%)分居第九、十名。

Gartner指出,人工智能基础设施的建设正在催生对人工智能处理器、HBM和网络芯片的强劲需求。2025年,HBM占DRAM市场的23%,销售额超过300亿美元,而人工智能处理器的销售额超过2000亿美元。预计到2029年,人工智能半导体将占半导体总销售额的50%以上。(校对/赵月)

2.机构:2026年8英寸晶圆代工产能利用率增长,厂商涨价;

1月13日,市调机构TrendForce在报告中指出,近期在台积电、三星两大厂逐步减产的背景下,AI相关电源管理芯片需求稳健增长,加上消费产品担忧下半年IC成本提高、产能遭排挤而提前备货,除了陆系晶圆厂8英寸产能利用率自2025年已先回升至高水平,其他区域厂商也已接获客户上修2026年订单,产能利用率同样上调,代工厂因此积极酝酿涨价。

TrendForce表示,台积电已于2025年正式开始逐步减少8英寸产能,目标于2027年部分厂区全面停产。三星同样于2025年启动8英寸减产,态度更加积极。TrendForce预期,2025年全球8英寸产能将因此年减约0.3%,正式进入负增长局面。2026年尽管中芯国际、世界先进等厂商计划小幅扩产,仍不及两大厂减产幅度,预估产能年减程度将扩大至2.4%。

该机构称,部分晶圆厂看好2026年8英寸产能将转为吃紧,已通知客户将调涨代工价格5-20%不等。TrendForce表示,与2025年仅针对部分旧制程或技术平台客户补涨不同,此次为不分客户、不分制程平台的全面调价。然而,基于消费终端隐忧,以及存储与先进制程涨价挤压週边IC成本等因素,8英寸晶圆价格的实际涨幅可能较为收敛。(校对/李梅)

3.艾为推出高防护高带宽小型化Type-C接口保护新品;

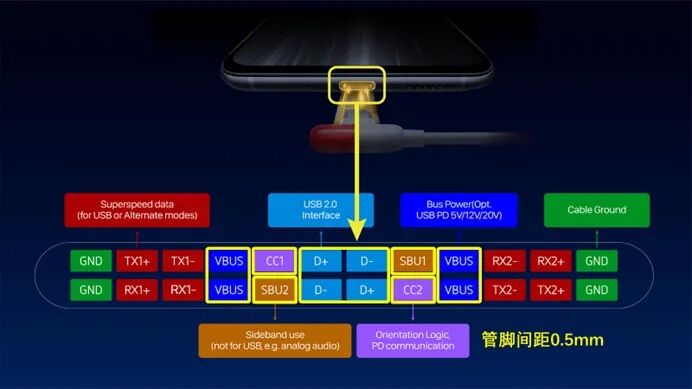

Type-C接口作为近年来普及的新型数据传输与充电接口,凭借可逆插拔、高速传输、快速充电、小巧易集成等优势,已成为智能手机、智能支付设备、可穿戴设备等领域的标配。然而,其物理尺寸限制和电气特性导致连接可靠性面临挑战:

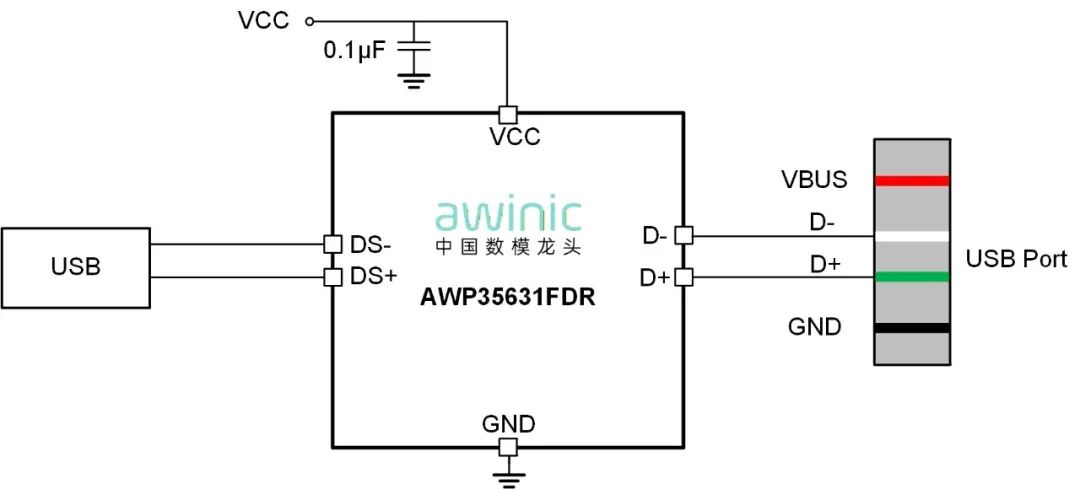

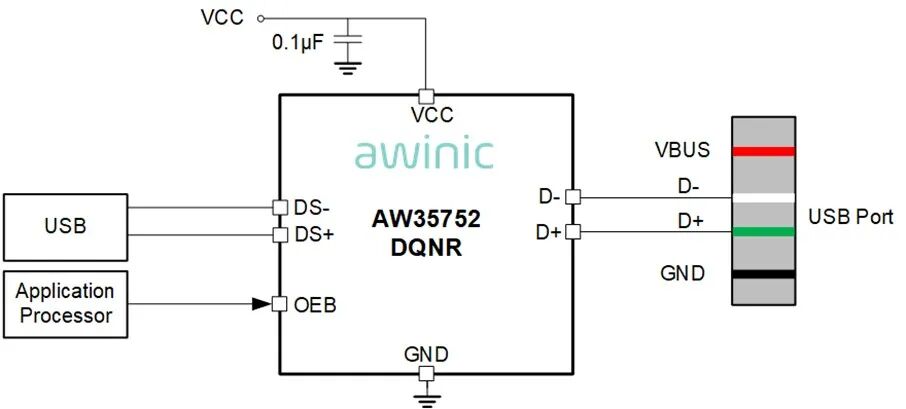

管脚间距小易引发ESD(静电放电)和浪涌冲击,造成电流失效;灰尘积累、温湿度变化或机械振动可能引发USB2.0 DPDM信号与Vbus/GND短路,威胁后级电路安全。针对这些痛点,数模集成电路龙头艾为电子推出AWP35631和AW35752D系列芯片,通过集成高鲁棒性防护、高带宽信号保持及小型化封装技术,为Type-C接口提供系统性解决方案。

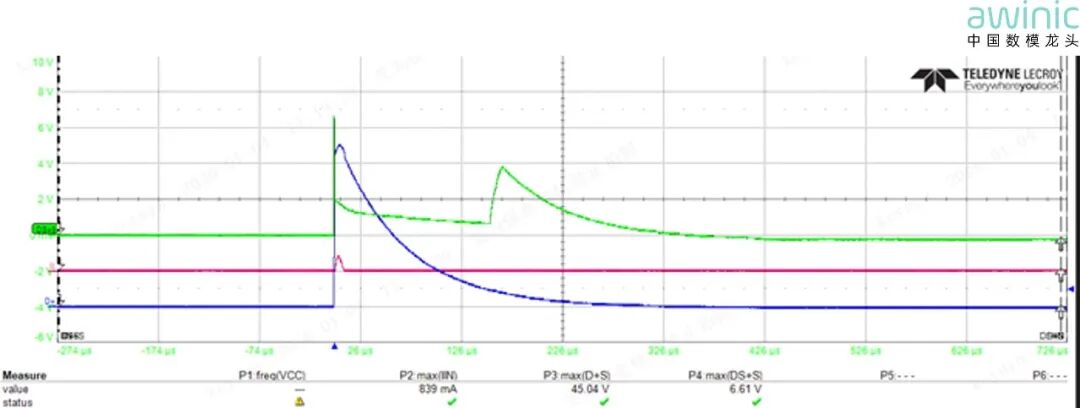

在半导体防护层面,AWP35631和AW35752D系列芯片集成8kV接触ESD防护、40V以上浪涌保护及快速过压保护能力。当发生+50V浪涌时,芯片可在500ns内将信号输出电压钳位至6.6V以下,有效避免后级电路损坏。其防护性能通过优化半导体材料与电路设计实现,例如采用低电容ESD保护结构,在保证防护等级的同时减少信号衰减。

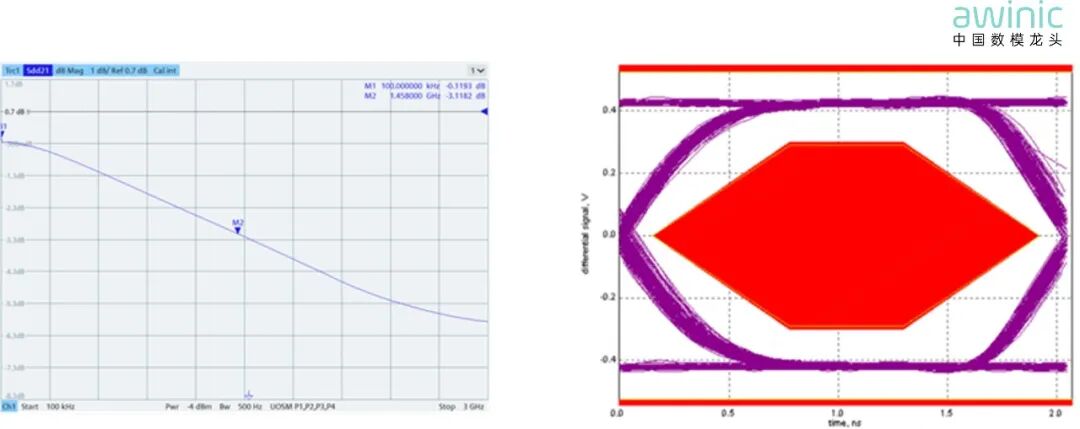

芯片设计突破了传统高防护与高带宽的矛盾。市面上多数产品通过增大芯片面积提升ESD和浪涌能力,但会导致输入端口Con(等效电容)和Ron(导通电阻)偏大,引发USB2高速模式下的插损增加和通信丢包。艾为电子凭借多年USB2保护开关技术积累,在AWP35631中实现1.4GHz差分带宽(-3dB)和3Ω典型导通电阻,确保信号完整性的同时满足防护需求。其核心在于采用低插损半导体工艺和优化版图布局,平衡了防护性能与信号传输效率。

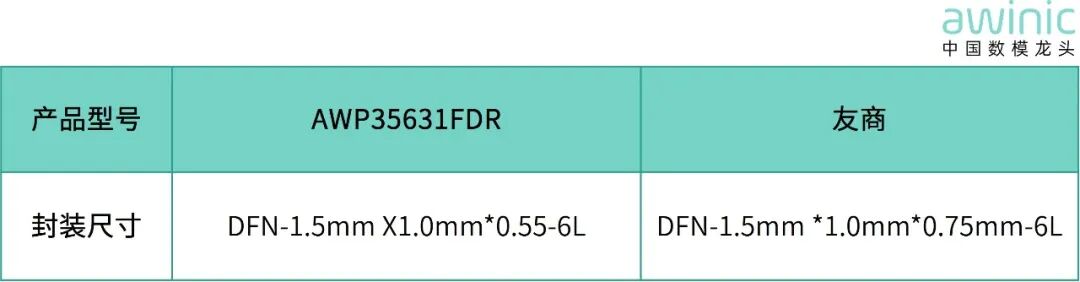

针对智能设备对芯片尺寸的严苛要求,艾为电子推出DFN1.5×1.0×0.55mm超小型封装AWP35631FDR,厚度较行业平均水平降低30%,特别适用于折叠屏手机和智能穿戴设备。该封装通过垂直堆叠技术和微米级引脚间距设计,在有限空间内集成多路保护电路,同时保持散热性能和机械可靠性。

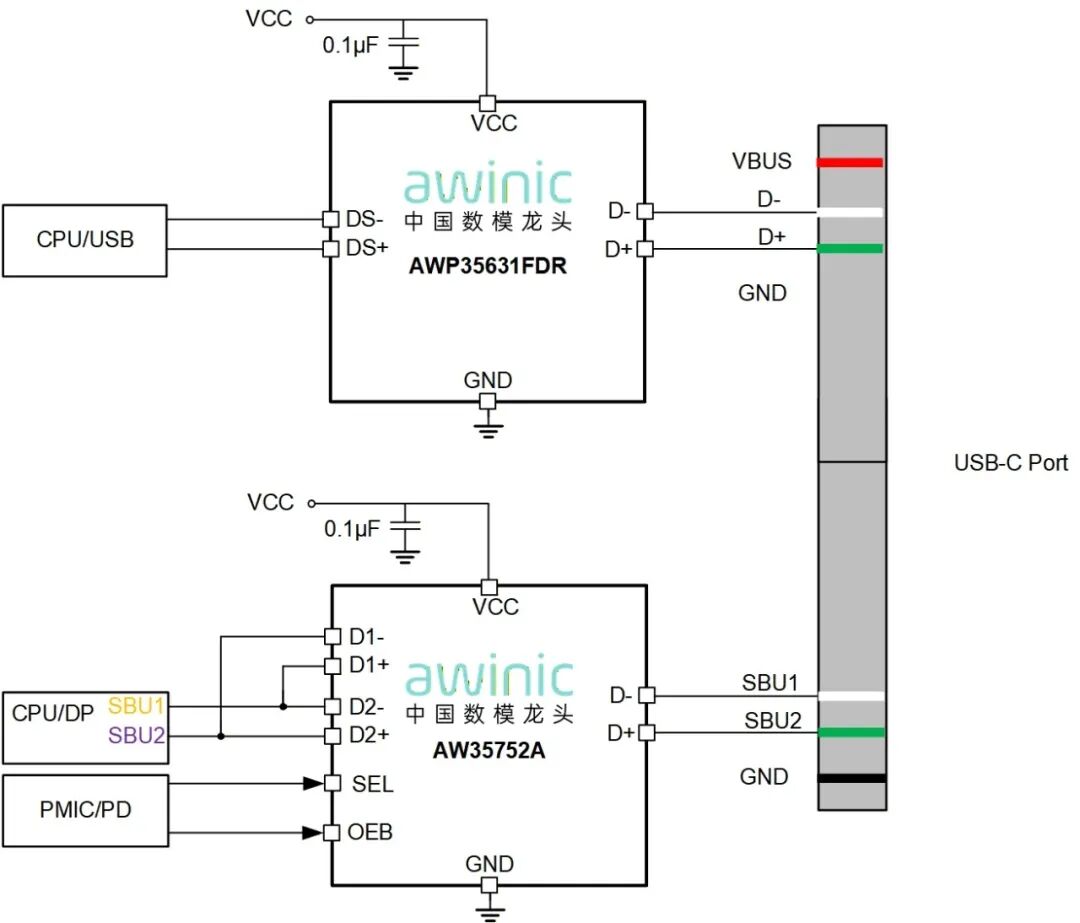

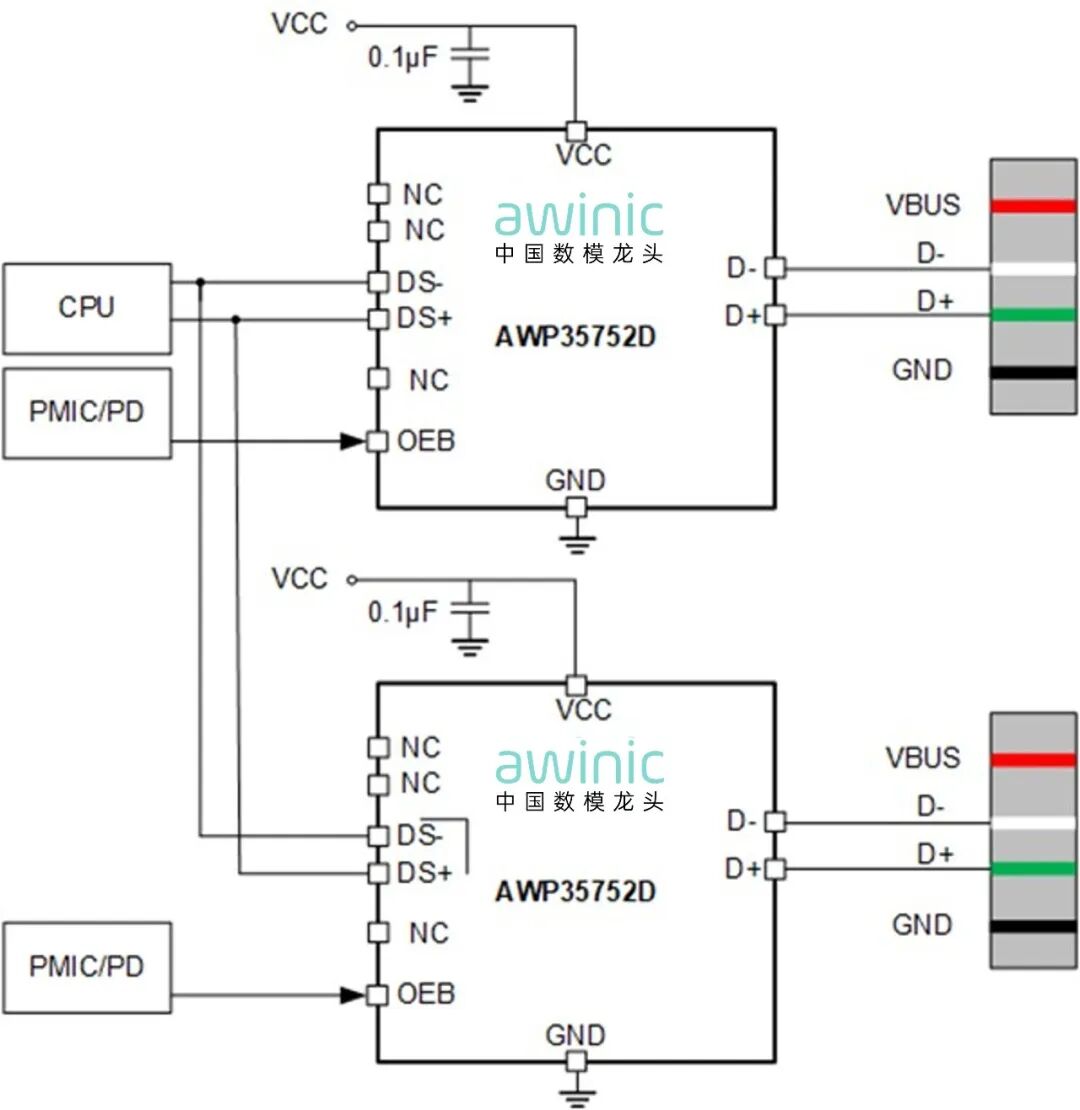

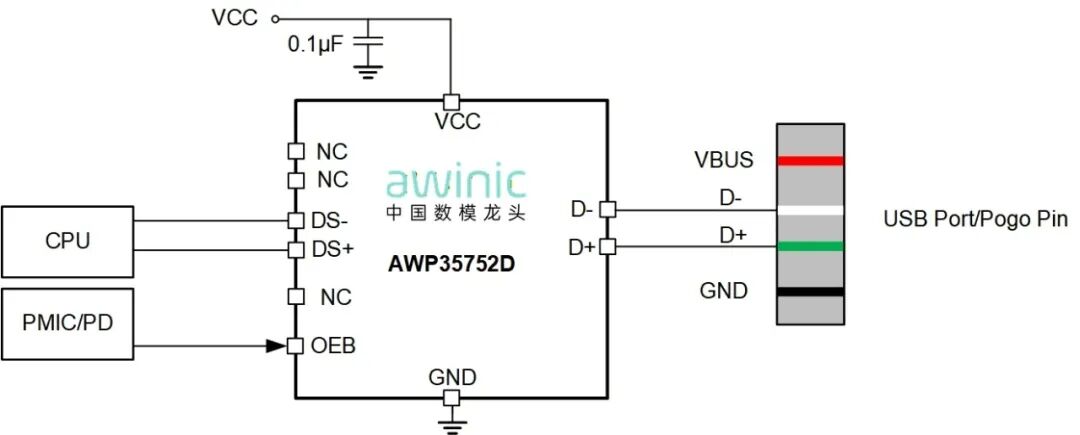

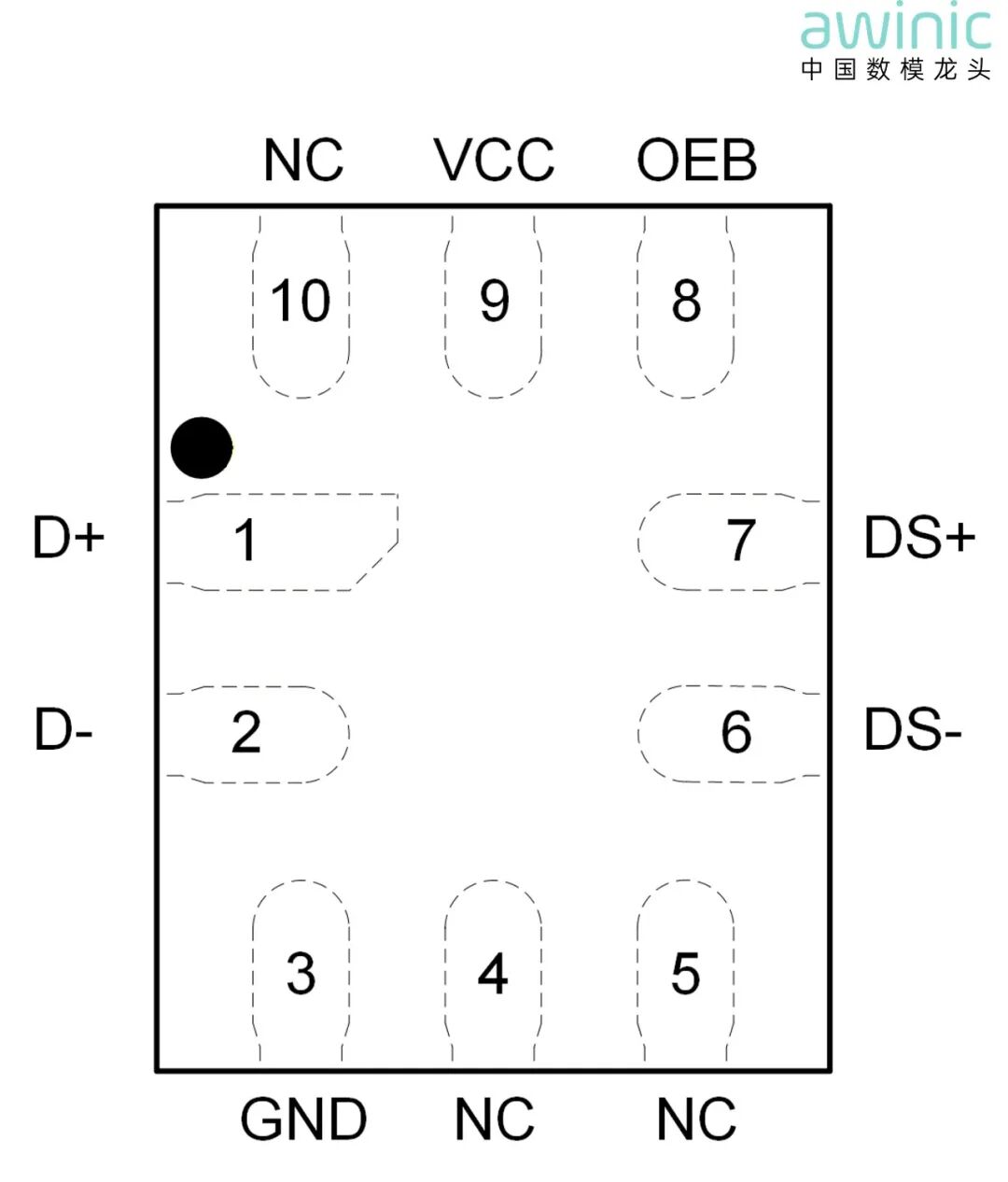

在典型应用中,AWP35631FDR与AW35752AQNR组合可实现智能手机Type-C接口的DPDM保护、DP投屏SBU保护及极性切换;AW35752D通过OEB引脚控制实现双USB2端口切换,满足智能支付设备单主控多接口需求;在行业PC领域,该芯片可通过物理断开USB2通道实现硬件级数据隔离,满足党政、金融等场景的安全要求。

技术参数方面,AWP35631支持1.2GHz单端/1.4GHz差分带宽,提供5.1V典型过压保护和36V DC端口保护,导通电阻3Ω,输入电容4pF,静态电流32μA,工作电压范围1.65V至5.5V。其封装兼容自动化贴装工艺,支持高速信号传输场景下的长期可靠性。

艾为电子通过半导体工艺创新与系统级设计,解决了Type-C接口在防护性能、信号完整性和空间限制之间的矛盾。其芯片方案已通过多领域验证,为智能设备接口保护提供了高集成度、高可靠性的半导体解决方案。

4.台积电将大幅增加在美投资 再建至少五座芯片工厂;

台积电

北京时间1月13日,据《纽约时报》报道,作为美国与中国台湾地区贸易协议的一部分,台积电将大幅增加在美投资,包括建设更多芯片工厂。

知情人士称,作为协议的一部分,台积电还将承诺在亚利桑那州再建设至少五座晶圆厂,这将使其在该州的工厂数量增加近一倍。相关投资的时间表目前尚不明确。

2020年以来,台积电已在亚利桑那州建成了一座工厂。第二座正在建设中,预计将于2028年投产。台积电之前已承诺在未来几年再建设四座工厂。现在,台积电同意再新建至少五座工厂。

另据《华尔街日报》报道,新规划的亚利桑那州工厂将生产逻辑芯片,即由英伟达、AMD等台积电主要客户设计、用于AI及其他先进计算的处理器。台积电还承诺建设两座新的工厂,用于生产被称为“封装芯片”的半导体产品,负责提供支持性功能。

截至发稿,台积电发言人拒绝对此置评。凤凰网