大家好,很高兴能与现场所有开发者们一起参加中国开发者大会。我今天演讲的主题是《从芯片到系统,赋能万物智能时代创新》。

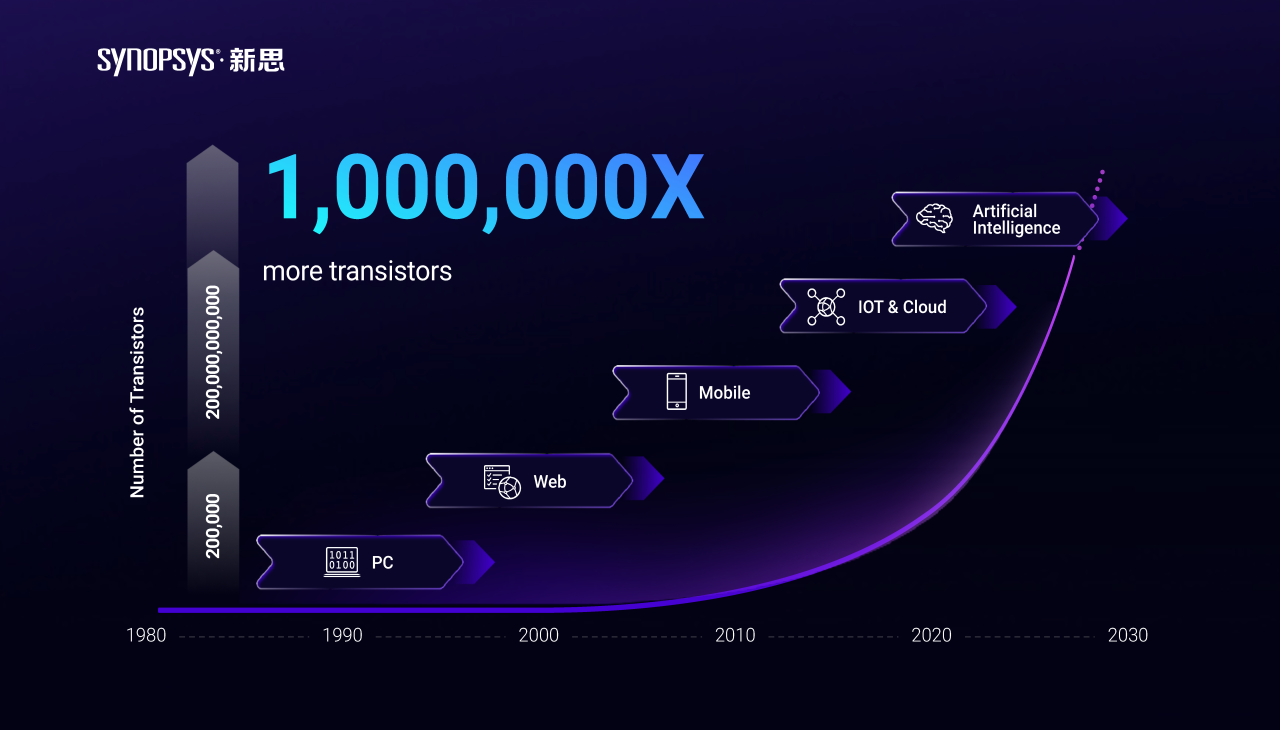

在谈论当前问题的复杂性与未来前景之前,让我们先重温一下过去四五十年的芯片发展历程。以前,复杂的SoC或芯片里大约有20万个晶体管,时至今日,市面上的一些AI芯片里晶体管的数量约为2000亿。也就是说,4、50年间,芯片上的元件数翻了100万倍。就复杂性而言,这是非常惊人的,而且我们也都知道,如果没有创新,这一切都是不可能的。

无论是晶体管级制造工艺、摩尔定律,还是助力半导体行业的合作伙伴和芯片开发者设计那些复杂系统而提供的EDA创新都必不可缺。如今,是什么推动了对这种复杂性的需求?我将这些因素称为转折点。在过去五十年里出现了几个转折点,它们分别涉及PC时代的性能优化,移动时代的功耗和性能优化,以及现今人工智能领域所需要的多维度优化──既要关注性能、功耗和成本,更要关注安全性、工作负载效率等直达最底层芯片的复杂需求。而就复杂性而言,接下来大家会听到我多次谈及关于设计这些系统的速度和复杂度挑战。

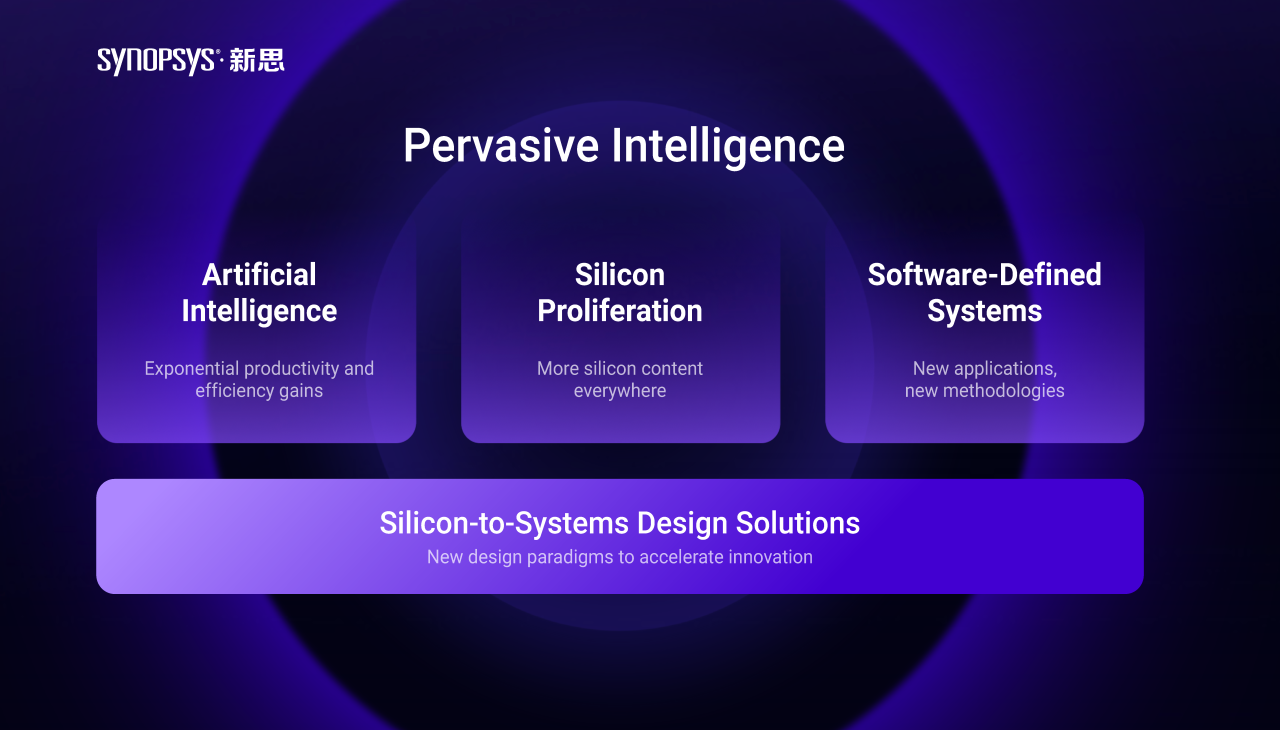

为什么要这样?驱动力是什么?如果您仔细观察人工智能──我们是人工智能的“推崇者”,我相信在座诸位也是──您会发现人工智能将改变人类的生活方式、人与人之间的互动方式以及人类与机器和系统之间的互动方式。当我们之间进行互动或与所使用的系统交互时,它确实会改变并提高我们的生产力和效率。现在,这些系统离不开芯片的支持,那么,芯片的大量普及是实现AI大规模部署的必要条件。

不妨畅想一下,未来每个系统将如何成为智能系统。这意味着什么?如果系统是一部汽车、一台手机或是您的智能家居,您当然希望这个系统能够支持AI,能够智能互联。为此,您希望用先进的芯片来驱动它。并且系统要由软件来定义,这正是我们整个行业所面临的大好机遇。我们将此称为万物智能时代,而AI是其中的关键驱动力,芯片则用于支持和驱动应用,从而让每个系统都更加智能。这种复杂性以及芯片与系统之间的连接都要求采用不同的方法来设计芯片和系统,这将是我本次演讲的重点。

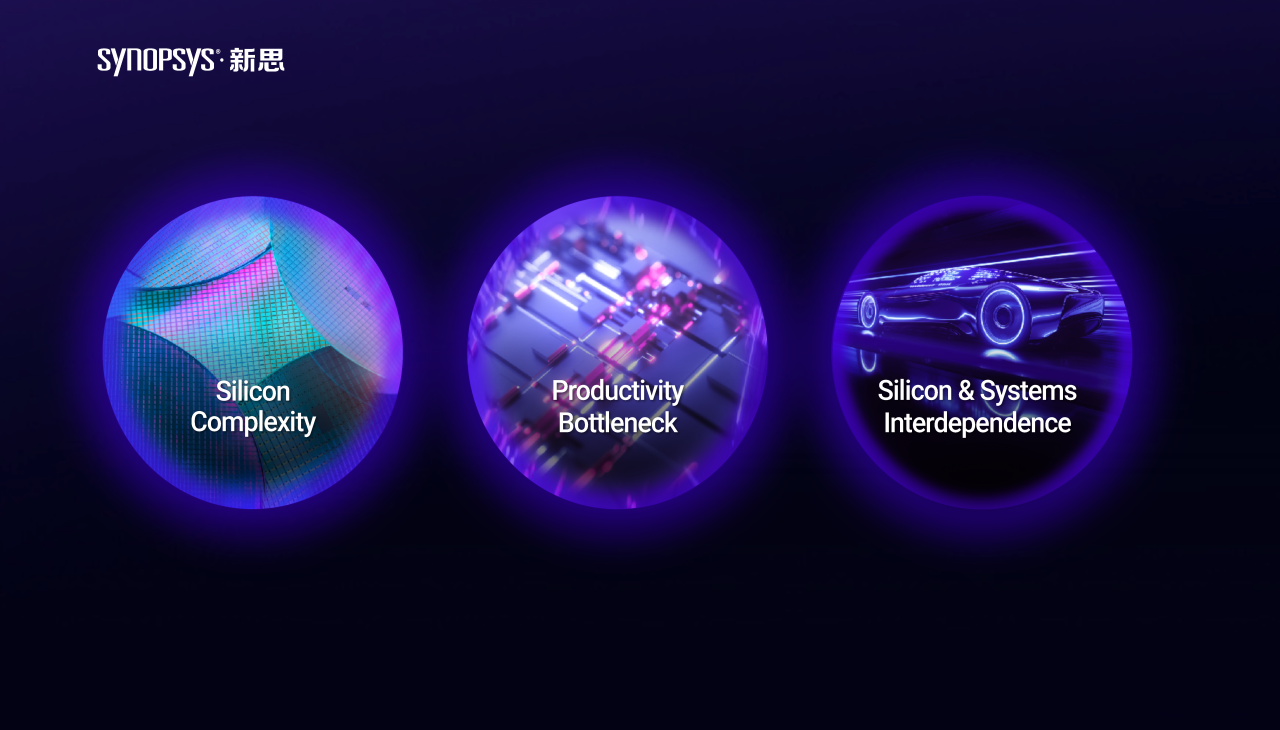

万物智能时代的三大挑战

就挑战而言,我们这个行业从第一天起就一直在应对各种挑战。当一枚芯片上有20万个晶体管时,其实已经很复杂了。而随着摩尔定律的发展,一枚芯片上将会有2000亿个晶体管,这就更加复杂了。我们这里要谈到整个行业面临的关键挑战,涉及芯片复杂度和生产力瓶颈──您不能仅仅干等着,希望18、24、30多个月后就能得到芯片──那是不可能的。回到开发节奏上,尽管复杂性呈指数级增长,但芯片的开发节奏和速度需要提升。第三个方面是芯片与系统之间的相互依赖性,以上就是整个行业面临的三大挑战。接下来我将逐一详细说明,明确其中的主要问题,并介绍新思科技为支持产品创新而付出的努力。

首先,芯片复杂性。我前面多次提到了摩尔定律,摩尔定律仍在发挥作用。我们正在从纳米时代走向埃米时代,我们称之为“向埃米级演进”。现在,围绕摩尔定律,有一件事已然发生了变化──回顾过去的10年、15年,我们客户的客户,也就是系统公司,往往会基于摩尔定律规划下一个产品版本的功率、性能和成本,我们可以明确知道从一个工艺节点到下一个工艺节点所能实现的性能、功耗和成本。

但现在,一切都变了!当然,这并不是说摩尔定律已经失效,而是说摩尔定律的可预测性以及经济性和成本都发生了巨大变化。为了支持产品创新,出现了一个新的优化要素,我们称之为“向万亿级演进”。为了实现想要的性能、功耗或功能,还可以使用其他哪些方法?将更多的晶体管塞到系统中?现在,我们将芯片设计解决方案分为三个方面以支持向埃米级和万亿级演进。

打造超融合创新平台,助力芯片设计向万亿级时代迈进

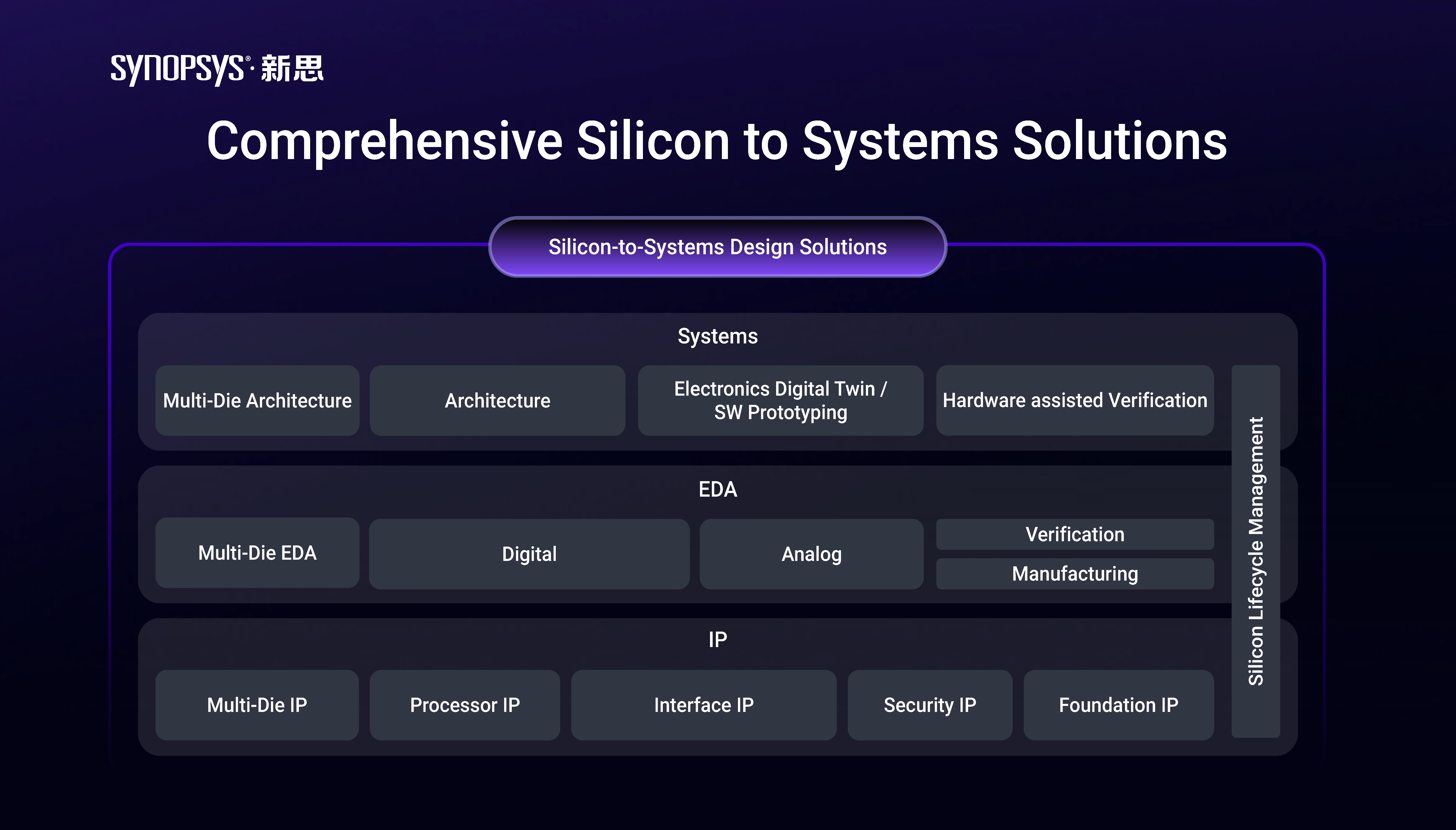

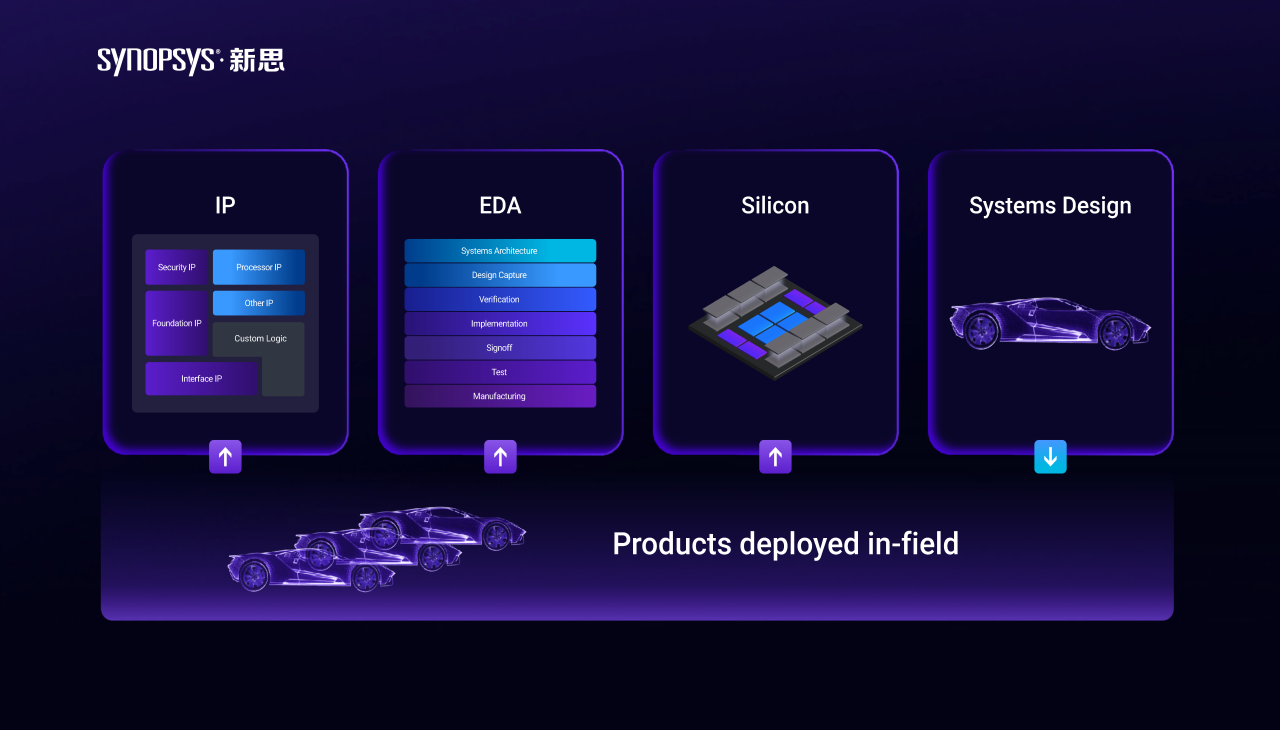

首先,如果您仔细留意目前的任何高级SoC,就会发现大多数SoC都采用标准接口,包括UCIe、PCIe、DDR和HBM等,这些都属于标准接口。这些标准化的东西并不是客户所关心的,客户在意的是如何使用资源让产品具有差异性。新思科技拥有值得客户信赖的广泛IP核组合;第二个方面是EDA平台,毋庸置疑的是,如果没有EDA来处理设计的复杂性,那些先进的芯片也就不复存在。因此,必须围绕EDA不断创新。第三个方面是高级封装,也就是先进的Multi-Die解决方案,能够提供所需的万亿晶体管容量,以此满足不同应用的需求推动芯片发展。

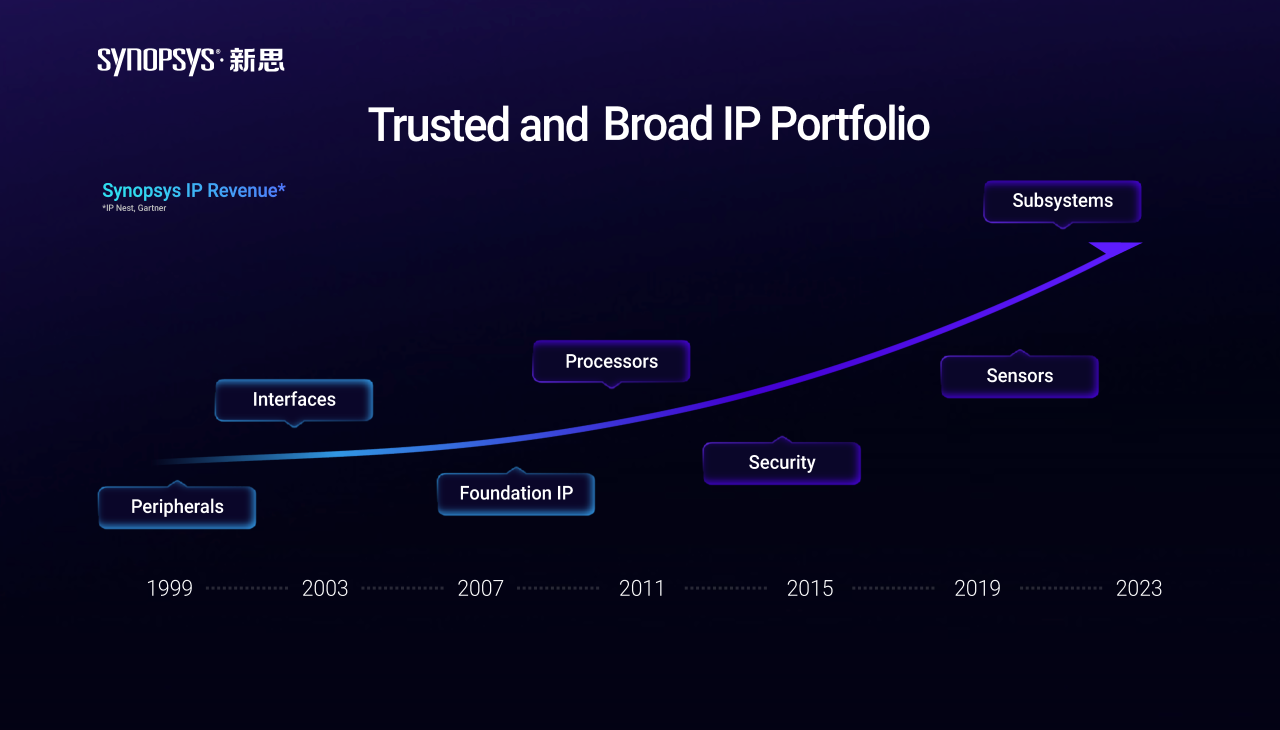

现在,让我们先从IP核组合说起。新思科技从事IP业务已近26年。最初,我们主要提供Design Compiler所需要的小模块,因此,在综合时您无需自己从头设计,加法器或乘法器。我们有一个这样的库,我们称之为外设IP,随后逐渐扩展到接口IP、基础IP、安全IP、处理器IP,一直到子系统IP。例如,一个包含控制器和PHY及其相关逻辑的子系统IP,这是芯片的重要组成部分,客户通常没兴趣设计这些部分。因为过于复杂,他们也不太想在这个地方投入太多资源和精力。

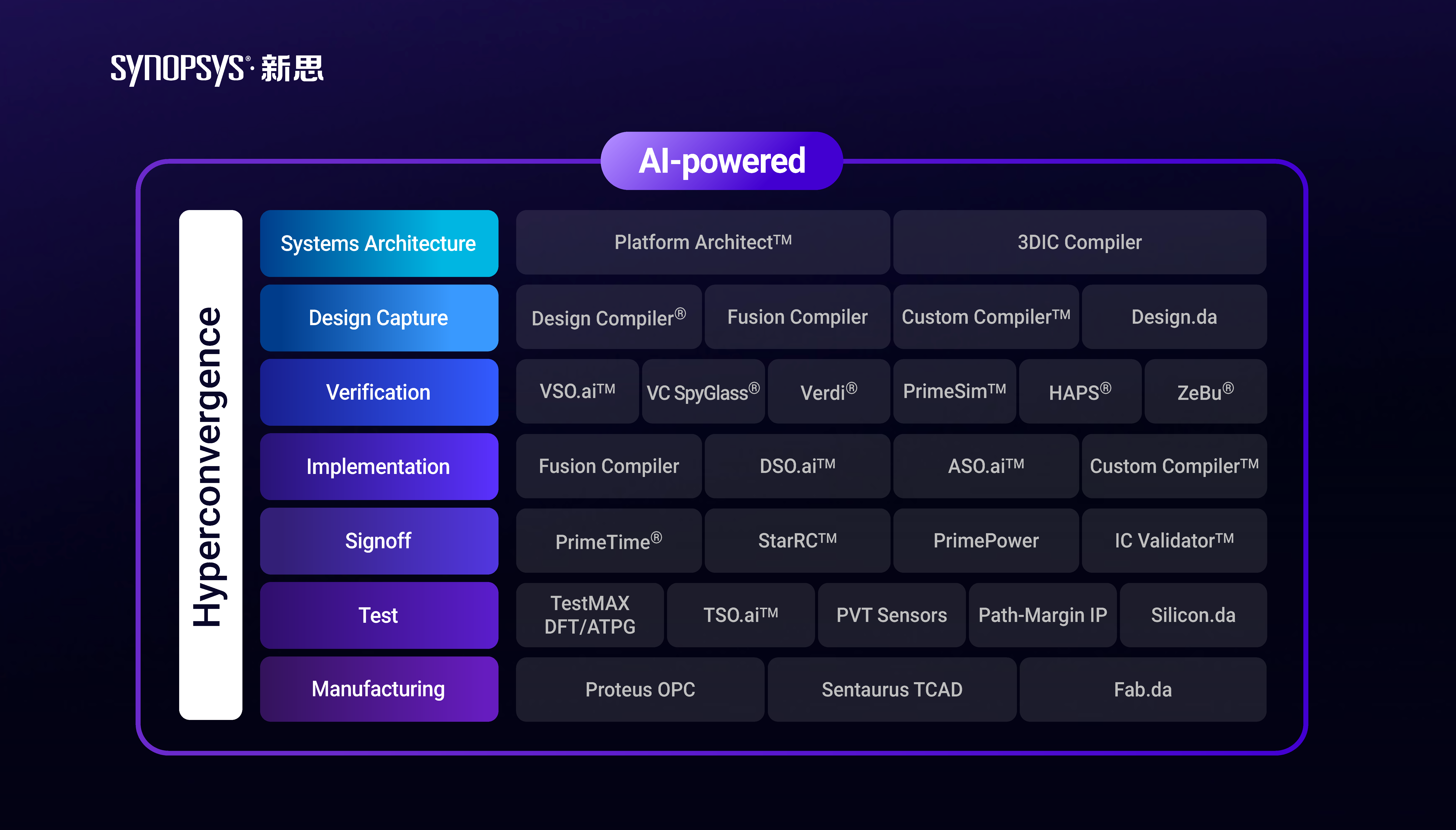

今天,作为接口IP的全球领先企业,我们致力于为客户提供包罗万象的IP核组合。对此我们倍感自豪,同时也要感谢大家的信任。在EDA平台方面,新思科技具有显著优势,可以打造真正的端到端EDA平台,从TCAD晶体管器件级建模和仿真工具,直到Platform Architect系统级设计工具,以及居于两者之间的一切,这是一个端到端解决方案,也是新思科技的特有产品──即一个涵盖系统架构、设计捕获以及签核、测试和制造的全面端到端解决方案。

我们在大约七八年前就投资了对芯片时序、功耗和可靠性等复杂特性进行整体综合考虑的方案,也就是大家现在所说的EDA平台超融合──它能够在流程的每个步骤中研究,哪些引擎是可以共用的。我们会融合这些引擎,以便为客户提供可预测性,助力其确定该流程的最佳PPA,这就是Fusion Design平台。它以数据交换和公共引擎为基础,旨在提供可预测性更强、性能更优的PPA。

近几年,大概2017年,我们不断对其投入研究,使用强化学习等技术对EDA工具进行升级并一度引领AI发展,在芯片设计的诸多领域都可以利用AI来缩短设计时间,以更快地交付芯片。另外,在如何实现更优PPA在这方面,让我们来看一段台积公司的视频,就刚才我所介绍的内容分享相关经验。

现在让我来谈一谈芯片设计解决方案的第三个支柱,即先进的Multi-Die解决方案。行业也称之为高级封装。为什么需要这个解决方案?我们不可能将1000亿、2000亿个晶体管或甚至一万亿个晶体管设计到单个裸片芯片中。我们需要将不同的功能分解到不同的裸片芯片里,然后思考如何将其封装在一起。为了实现所需的功能,还需使用一些使用不同的工艺技术,甚至来自不同代工厂的裸片芯片。

几年前,我们推出了3DIC Compiler,它基于我刚才所述的融合数据模型而构建,在高级封装实现方面走在行业前沿,我们的客户用它来设计和实现自己的系统级封装,客户考虑在先进封装中使用Multi-Die时,他们需要决定怎样将整个架构设计在一起,这个就叫3D或2.5D异构集成。在这方面,3DIC Compiler可以大显身手。

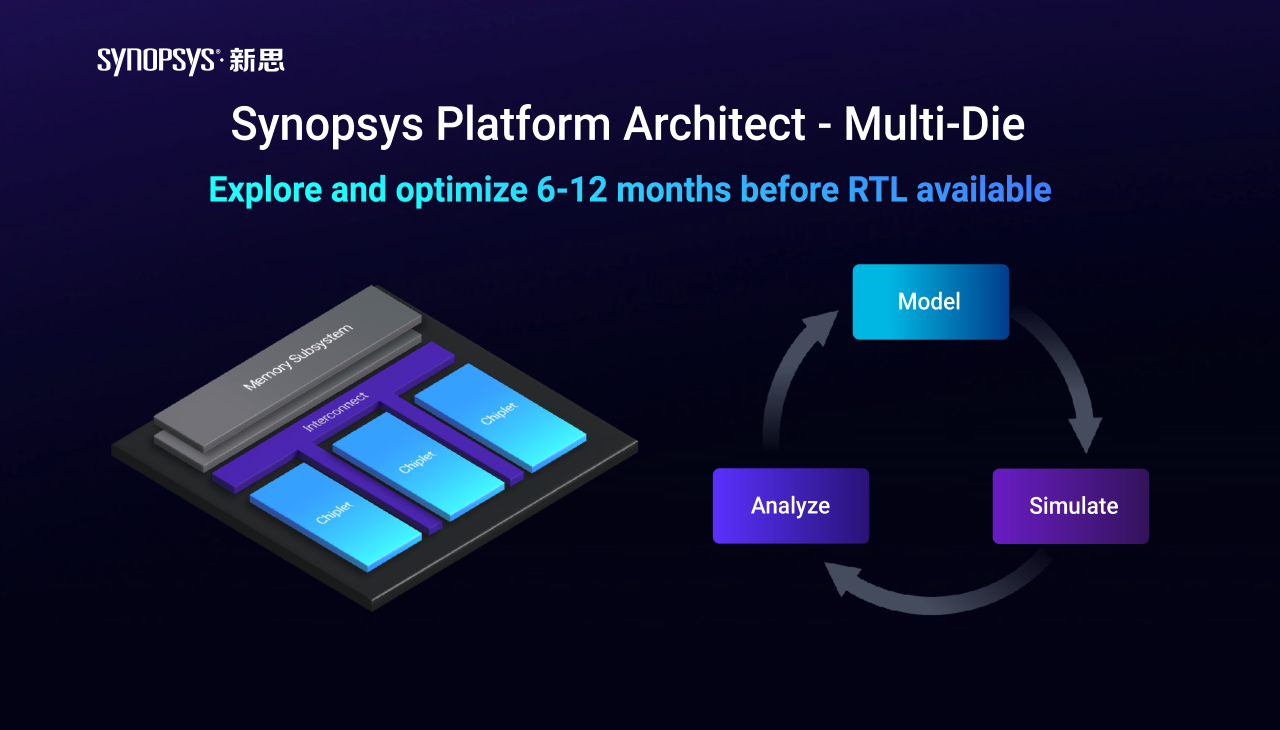

另一部分要做的是,如何使用新思科技 Platform Architect来设计系统或平台,它让您可以针对裸片芯片进行建模,展开仿真和分析,并在RTL可用之前,再次对不同裸片芯片的选择进行建模、仿真、分析,这就是我们的新思科技Platform Architect Multi-Die技术。

现在,让我们具体来看看先进封装和Multi-Die解决方案领导者的经验。

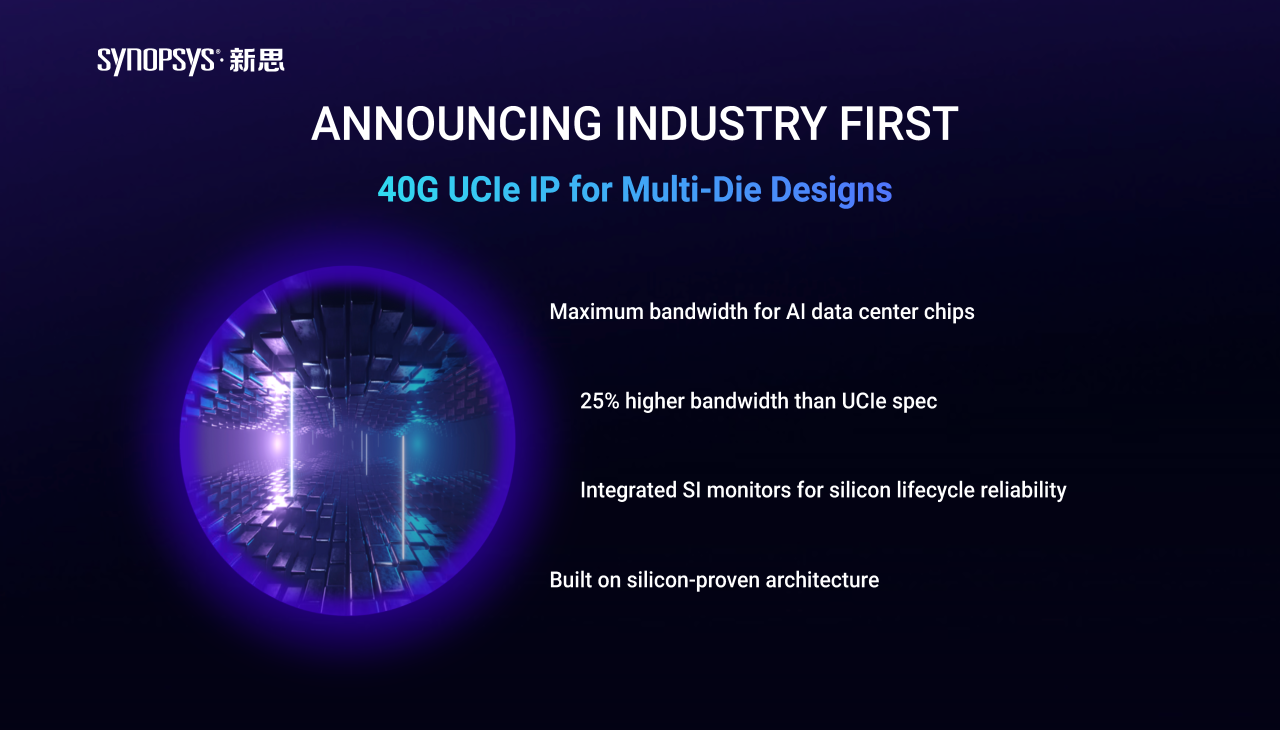

我们已宣布率先推出用于Multi-Die设计的40G UCIe IP,为什么这至关重要?比如一开始做了单芯片的设计,然后又想分解成多芯片设计系统,那么一定要避免避免带宽损失,避免功耗增加,以及避免面积增加,其中最重要的是:带宽!带宽!带宽!这是多芯片设计的关键挑战。

利用40G UCIe IP,将能够实现比UCIe规范高25%的带宽,它还集成了许多SI监控器,有助于提高芯片生命周期可靠性。稍后我会详细介绍这一点,将多个裸片芯片放在一个高级封装中时,这一点很重要。因为在现场运行的系统需基于不同工作负载。您应如何知道哪个裸片芯片或小芯片导致了可靠性故障,因此,在每个裸片芯片上安装监控器和传感器,并确保能够在系统级别进行连接和监控,这一点不容忽视!借助40G UCIe IP,我们不仅能够提升带宽,它还集成了能够提高可靠性的先进监控器和传感器。

全球领先EDA+IP解决方案,持续加速合作伙伴提升生产力

在讨论完芯片复杂性之后,让我们来关注生产力瓶颈,这一点无需多言。之前我反复谈及两个词──速度和复杂性。这些芯片的设计复杂性,给我们的客户带来了很大压力,以至于他们绞尽脑汁,想了很多方法来提高生产力。他们必须充分利用现有资源和研发投入,来按时交付这些差异化芯片。

首先是IP,正如我之前提到的,其实大多数的客户都可以自行投入研发,并打造与新思科技所提供的相同功能的IP。但问题是,这是一种正确使用资源的方法吗?又是否有助于实现差异化?如果答案是否定的,那么可以考虑采用新思科技在基础IP、安全IP、接口IP以及其他许多IP(包括处理器)等广泛的IP产品组合。

另一个生产力助推器是AI,我们将我们的AI产品命名为Synopsys.ai。那么,什么是Synopsys.ai?其中包含三个要素,第一个要素是AI驱动的优化,它真正着眼于设计空间优化,并利用许多技术来更快地提供更好的结果。DSO.ai是我们在2020年左右推出的第一项Synopsys.ai技术,随后还推出了验证空间优化VSO.ai、即测试空间优化TSO.ai、模拟空间优化ASO.ai。这里展示了一些成果,侧重于提高PPA并有效缩短设计时间,包括更好的覆盖率和更优的测试向量,其目的是降低测试成本、缩短测试时间。而ASO.ai则与复杂模拟设计的周转时间有关。

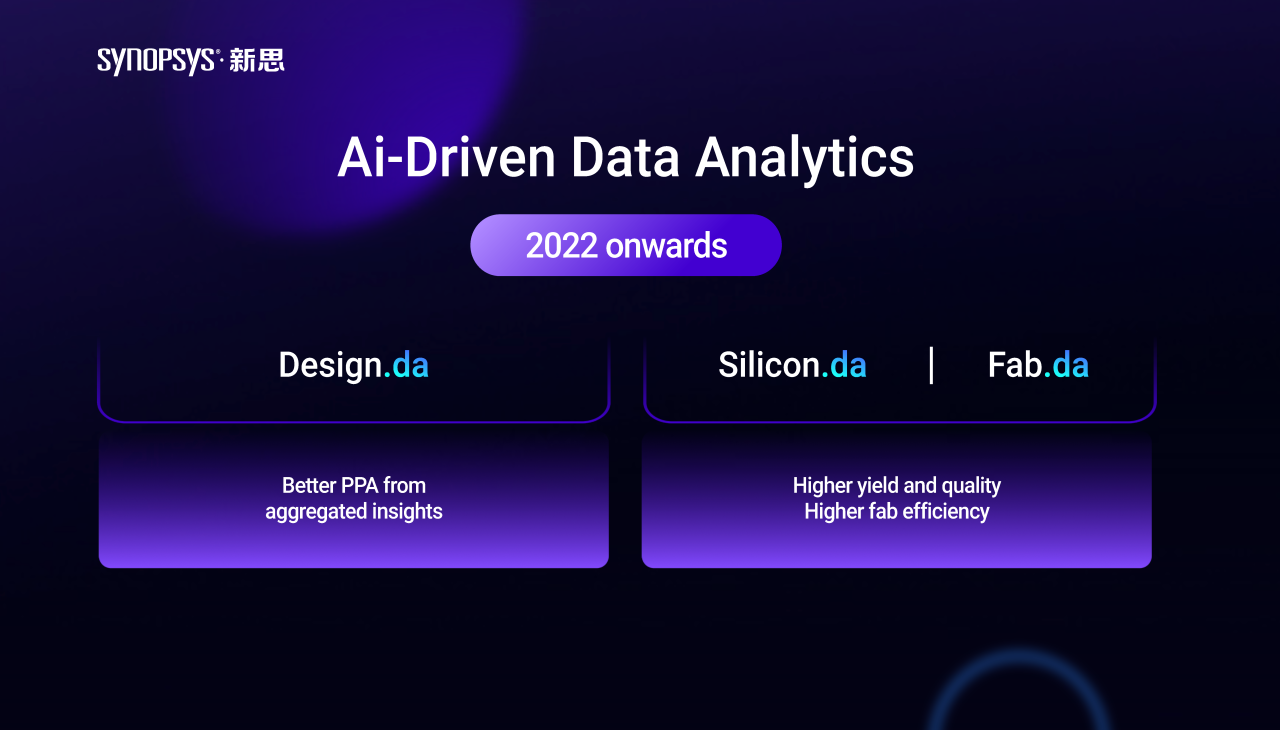

第二个要素,如果您仔细留意端到端芯片设计流程,就会发现设计流程的各个步骤使用了一个一致数据集,如果能从第三步中获得相关的关键数据,那么就可以回过头来优化第二步或第一步。从流片前到流片后,再到制造阶段的过程中,哪些关键数据有助于优化和交付更好的产品?当然,这其中既有正在开发的产品,还包含更出色的衍生产品,这就是我们的数据分析工作。我们提供了Design.da、Silicon.da和Fab.da。Design.da更多地侧重于流片前,可以根据汇总的关键数据来优化PPA,Silicon.da和Fab.da则侧重于提升晶圆厂良率、质量和效率。这些就是我们的.da技术。

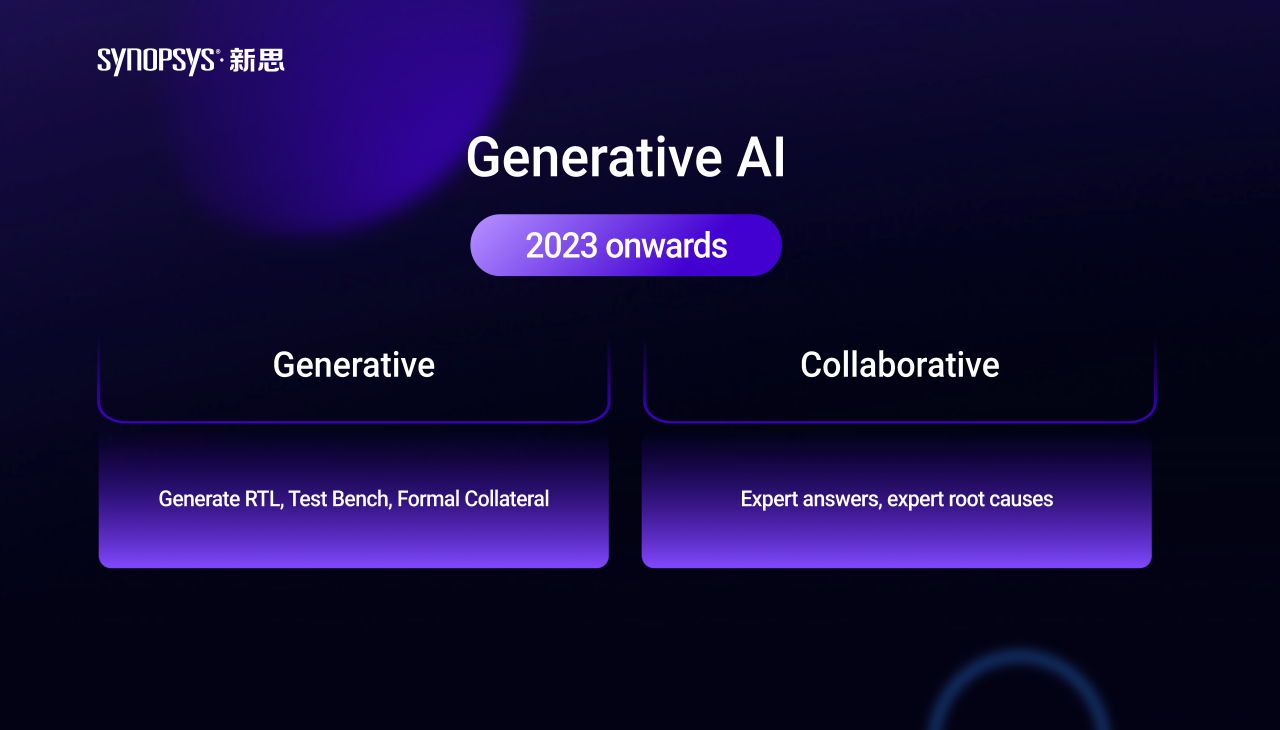

第三个要素是生成式人工智能(GenAI),我们在2023年就开始了相关工作,对于生成式AI来说,问题在于哪一部分设计流程可以真正使用生成式AI工具Synopsys.ai来生成代码,而无需进行开发和人工操作,或能减少到更低限度?在不同的开发阶段,我们正针对几个方面进行探索:例如,是否可以将Copilot概念用于RTL,从而生成RTL代码或测试平台,或者进行形式化验证和检查?这就是我们在早期客户参与的各个阶段研发的生成性示例。另一方面则是协作,我们可以将其视为新思科技工作流程的AI助手,比如,开发者可以得到一个熟悉LLM的AI专家,并与之进行交互协作,提供最佳建议以及找出导致当前问题的根本原因。

从芯片到系统设计解决方案,赋能智能汽车等广泛系统级公司创新

前面我们讨论了芯片复杂度、讨论了生产力遭遇瓶颈,最后要谈的是芯片与系统之间的相互依赖性。过去三到四年间芯片开发的加速发展过程,我们看到一家芯片公司很可能不再制造面向众多市场的通用芯片,而一家系统公司,也不能简单地认为可以从任何供应商那里得到用于数据中心、汽车、手机等终端产品的芯片并期望这些产品能够脱颖而出。

当前,由于系统的要求日益复杂,芯片与系统之间的定制化以及两者之间的关联变得越来越紧密。以数据中心为例,数据中心所面临的大型挑战不仅是其本身的成本或性能,还有数据中心的能效。面向不同应用的数据中心,如购物、观影平台或运行EDA工作负载的数据中心,都非常不同。因此,我们需要不同的优化方式来处理从工作负载到芯片设计的工作。

现在,我想向大家进一步展示开发工作流程。当谈起芯片、软件、系统以及这些不同阶段的相互依赖性时,这具体是如何运行的?工作流程又是什么?这就要从系统要求说起──我指的是电子系统要求,大家也可以将系统理解为汽车。开发者应如何预先设计和构建这些电子系统要求?这些系统要求将定义软件需求与硬件需求,因此,一旦确定了汽车电子设备的系统架构与目标,也就能决定软件需求的类型并得到硬件需求。

通常,瓶颈出现在软件开发阶段。从历史经验来看,软件开发总要等到有实际的芯片和硬件才能推进设计流程,但这个等待的时长?如果谁能把它缩短,谁就能带来显著的生产力。为了缩短这个等待的时长,就需要硬件或芯片的数字化表达。确定了硬件需求后,就可以开始定义芯片架构,比如,要不要用Multi-Die架构?如果要,用哪种技术?在功耗以及性能方面,期望达到什么样的目标?如何将其整合在一起?因此,由软件需求驱动的芯片需求将开始定义软件和芯片设计的下一个阶段,软件和芯片设计同步开发后就会推动虚拟化或数字孪生的发展,在软件开发的过程中,软件开发者能够得到更实时、更准确、更真实的更新信息,而将所有这些组合在一起,也就是我们所说的,芯片与软件之间的完整的电子系统。

对于数字孪生和虚拟化以及芯片和系统的生产力解决方案层面,新思科技能够提供许多行业领先的技术换个解决方案。它们构成了芯片和系统之间、硬件辅助验证、Synopsys.ai及其他产品之间的桥梁。当然,还包括我之前所介绍的芯片IP。现在,我们持续推出全面的芯片到系统解决方案,也是为了优化系统要求和所需芯片之间的匹配度,反之亦然。

对于一家芯片公司,如果希望确保提供更具竞争力、更符合系统要求的芯片,就需要用到IP、EDA和上述系统工具。我们可以来看看芯片生命周期管理(SLM),我刚刚说到40G IP时也提到过,这些是放在芯片或小芯片中的监控器和传感器,可以监控芯片的多个指标,包括软件安全、散热情况、以及PVT等芯片其他方面的关键指标。说到电子数字孪生时,我们会想到非常多例子,但鉴于我们一开始讨论了汽车,那就让我们继续来关注汽车。

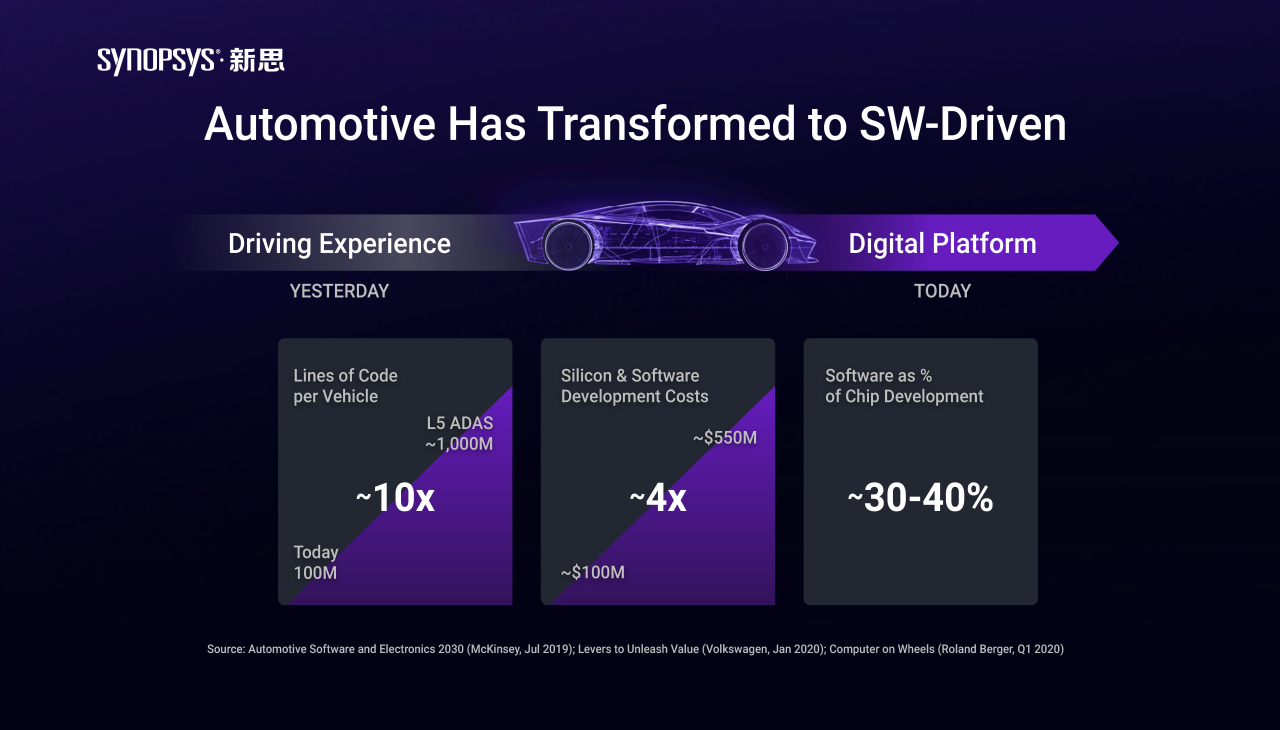

回顾汽车行业的巨大变化,以一辆L5 ADAS自动驾驶汽车为例,汽车中的代码行数需要从现在的1亿行,其实这对汽车来讲已经是海量,增加到大约10倍。芯片开发难度、芯片成本和软件开发成本都在急剧上升,于是,汽车行业OEM正在加速投入到芯片和软件研发领域,而芯片投资的占比显著增加。

那么,应如何实现汽车电子系统虚拟化呢?就像构建芯片、片上系统以及数据中心一样,现在汽车所采用的方法与此类似,其中包括使用虚拟区域控制器来控制汽车的各个方面,同时还有中央计算单元、集成能力、以及感知外部环境并采取行动的能力。随着汽车向L3、L4、L5自动驾驶发展,错综复杂的传感和驱动系统在先进汽车中变得举足轻重。

顺便说一句,同样的方法也适用于许多先进的智能系统,包括工厂车间的机器人以及数据中心。可以看到,同样的概念和方法在汽车领域正蓬勃发展,图中紫色部分是新思科技目前提供的解决方案,还有就是我们如何与生态系统合作,我们致力于将整车电子系统的虚拟化组合在一起。大家可以从蔚来的视频中具体看一下我们的合作经验。

EDA+IP+Multi-Die+数字孪生解决方案,推动万物智能时代加速到来

我们现在可以总结一下,在提高生产力、处理先进系统的复杂性和速度要求等方面,IP是至关重要的部分。人工智能驱动的超融合EDA流程,对于简化、支持和加快客户研发以及提高开发效率不可或缺。在芯片和先进封装方面,将这些Multi-Die以及Multi-Chiplet分解并集成到先进封装中,一定是未来在芯片系统中实现更多复杂功能的关键。在考虑系统设计,也就是芯片与系统之间的桥梁时,需要考虑芯片生命周期管理。因为系统一旦投入实际使用,就需要确保其可靠性,并保证现场应用的反馈能够回到驱动系统的芯片中,这两点非常重要!

总之,我们正处在AI的关键转折点,这是一次重大的转型,AI或将参与到公司内的所有工作流程中,不断改变我们参与、运营、开发产品以及与生态系统互动的方式。无限的机遇就在我们眼前,而要想利用好这些机遇,我们该如何适应、改变和转型?

在这个过程中,新思科技将成为值得大家信赖的合作伙伴,我们致力于提供全球领先的先进技术和解决方案,助力合作伙伴提高开发效率,加快开发速度、不断迭代技术并交付创新产品。非常感谢大家对新思科技的关注,也谢谢大家的宝贵时间。再次感谢大家选择与新思科技合作,以及对新思科技的信任,谢谢大家!