近日,芯砺智能正式发布全自研Chiplet Die-to-Die互连IP(以下称CL-Link)芯片一次性流片成功并顺利点亮,该芯片是人工智能时代片间互连最优路径,能完美地实现高带宽、低延迟、低成本、高可靠性及安全性,可以广泛应用于智能汽车、人形机器人、高性能边缘计算、服务器等多个领域。这一重大里程碑将为人工智能时代算力基础设施建设带来更加多元灵活的互连解决方案,也标志着芯砺智能在后摩尔时代异构集成芯片领域的领先地位。

芯砺智能全自研CL-Link兼有并行互连技术的高带宽、低延迟和串行互连技术的高可靠性、低成本的优势。CL-Link通过一种用于片间互连的总线流水线结构,做到了以较小位宽来实现片间高带宽及低延迟的互连,每条信号速率高达16Gbps,其总线到总线的延时小于5ns,和片内总线延迟在同一量级,可以支持不同处理器和储存器之间的低延迟互连要求,从而实现1+1接近2的高效联合计算效率,在Chiplet高良率及低成本的基础上实现算力灵活扩展。CL-Link的成功回片点亮是芯砺智能迈向高算力可扩展(200-2000 Tops)发展路径的基石。

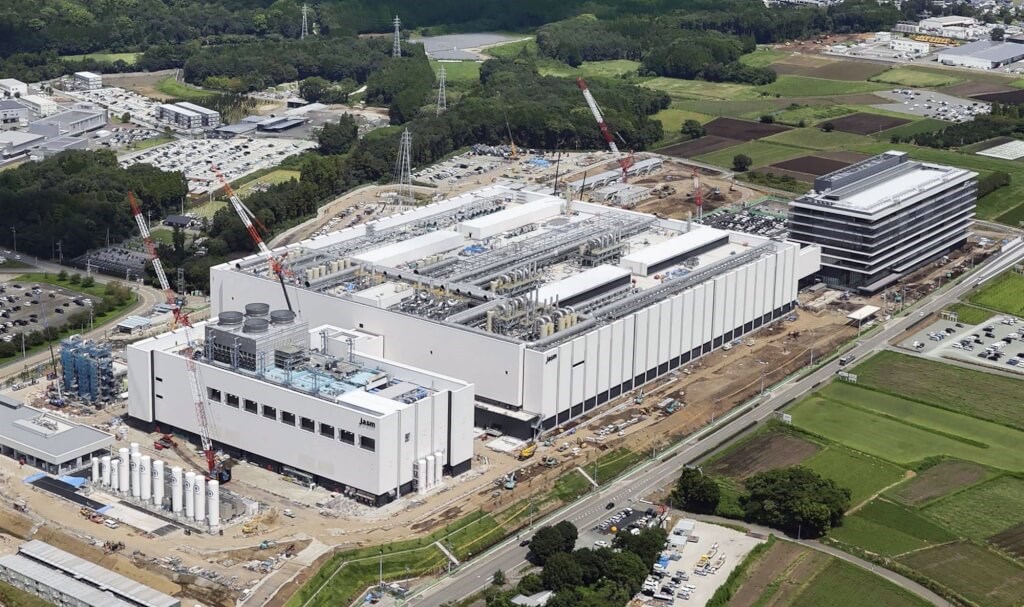

图:芯砺智能CL-Link赋能异构集成算力扩展

Chiplet异构集成芯片是后摩尔时代算力扩展的行业共识,但主流的Chiplet技术主要依靠先进封装,对成本、可靠性、功能安全及供应链安全都提出了较大的挑战。芯砺智能专利性的Chiplet技术可以凭借传统封装实现高性能算力扩展,当前芯砺智能基于传统封装的CL-Link技术已经获得全球首个车规级ISO 26262 ASIL-D Ready认证,可以通过小芯片搭积木的方式实现灵活可扩展的多元化产品矩阵,实现商业价值最大化。

图:车规级CL-Link ISO26262 ASIL-D Ready认证

图:Chiplet赋能:一个平台覆盖多个应用场景,实现产品灵活可扩展矩阵

芯砺智能全球首个车规级CL-Link的成功回片及点亮标志着芯砺智能在后摩尔时代异构集成芯片互连方面的先发优势。未来,芯砺智能将持续深耕人工智能时代的算力扩展普惠方案,加速算力基础设施建设!

登录

登录