集微网消息,随着晶圆代工制程不断缩小,摩尔定律逼近极限,在工艺制程难以进一步缩小的情况下,先进封装已经成为后摩尔时代的必然选择,如2.5D/3D封装、SiP(系统级封装)等先进封装技术等成为产业界重点推进的方向。但这也同步带来了芯片测试的挑战——由于先进封装的复杂度大大提升,里面可能会涉及包括存储、CPU、GPU等各类芯片,意味着测试的复杂度也随之大大提升。

爱德万测试业务发展部总监葛樑8月2日在第六届中国系统级封装大会(SiP China)上发表《先进测试技术助力先进封装发展》主题演讲,从先进封装技术的测试挑战以及测试技术的发展趋势等方面做了深入分析。爱德万测试近年来一直很关注先进封装,特别是2.5D和3D封装方面,并且已经和业内的合作伙伴一起开发了新一代测试技术,以满足2.5D/3D封装的测试需求。

先进封装技术是后摩尔时代趋势

“对于高性能芯片来说,2.5D/3D先进封装已经是标配。”葛樑在会上指出。进入后摩尔时代,伴随着CPU、GPU、FPGA等高性能运算(HPC)芯片性能要求持续提升,覆晶封装(Flip Chip;FC)、层叠封装(Package on Package;PoP)等传统封装技术已经不足以满足高性能芯片的需求,2.5D/3D等先进封装技术的需求逐渐增加。

据Yole数据显示,2021年全球先进封装市场总营收达321亿美元,同比增幅高于2020年。预计到2027年,全球先进封装市场总营收将增长至572亿美元,年复合增长率将达到10%。其中,2.5D/3D堆叠IC是增长最快的技术。

就SiP(System in Package,系统级封装)技术而言,这是一种基于SoC的新型的封装技术,它将一个或多个裸片及无源器件构成的高性能模块封装在一个壳体内。这些芯片和器件以2D、2.5D或3D的方式整合在一个衬底上,并具备一个系统的功能从而使封装由单一芯片进入系统级芯片。2.5D/3D芯片堆叠技术带来的高集成度,在实现更高性能的同时对芯片从测试也提出了前所未有的挑战。

如何应对测试挑战?

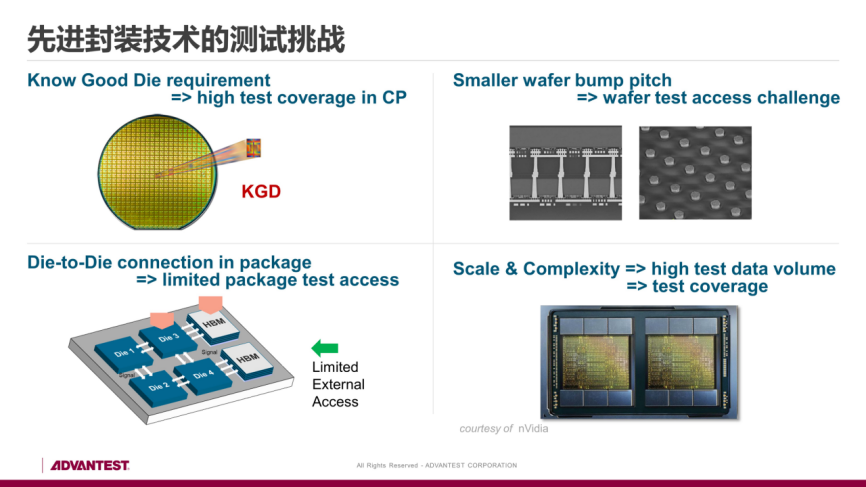

那么先进封装趋势给测试带来哪些挑战?

首先,在传统的测试,一块芯片通常在晶圆级测试层面测得比较简单,在封装完成后会测试得比较完整。但现在,由于先进封装的里面可能包含存储、CPU、GPU多个芯片,但凡其中有一颗不好的芯片,就有可能拖累其他所有的芯片,使得昂贵的封装付之东流。为了避免这种状况,很多原本在封装之后的测试需要提前至封装前,比如原来在后面做的系统级测试可能要提前到晶圆测试就要做,来保证整体的良率。

另一方面,2.5D封装时,原来在板级互联芯片,现在在封装级互联了,也就意味着很多的互联要从板级移到封装级。葛樑指出,这会带来芯片本身用户测试访问IO数的变少,“我们可以想象一颗GPU原来是要在板子上和memory相连的,所以它会有很多memory的 I/O,但现在它放在一个Package里面和HBM相连了,那么这些I/O就不需要存在了。这对芯片本身是个好事,但对测试来说就增加了挑战。因为测试就需要大量的I/O去访问芯片。

同时,由于芯片本身规模的快速上涨,以及新工艺需求的新测试类型的增加,测试需要的向量的总量有了大幅上涨。据预测,以2010年这个时间点来看,测试数据量随着时间上涨,大概以每2~3年翻一番的速度在提升。如果拉长到10年的跨度,大概要增加10倍。而类似HPC类的芯片又是最大规模,测试向量最大的芯片类型。

针对上述挑战,葛樑介绍,目前业内的测试解决方案主要从结构化测试和系统级测试两个角度着手。结构化测试,即针对芯片内部缺陷的测试。结构化测试里面最常用的就是Scan测试。2.5D和3D封装技术让Scan 接口的引脚数受限。这迫使Scan传输从原本的大量但低速的IO通道向更少的引脚数更大带宽发展。例如通过内部MUX(multiplexer,多路复用器)的方式让给原本传输率100M提升到 200,400,或800M。或者进一步,通过 高速接口(HSIO)的技术让传输测试向量,速度能够提升到几个Gbps。

据葛樑介绍,“这些芯片结构的改变对ATE测试设备来说,意味着要求更高的速度和更大的数据向量存储能力。爱德万测试在去年推出的新一代V93000 EXA Scale平台,能够轻松应对目前市面上所有主流的AI,HPC芯片的测试需求。随平台发布新的通用数字板卡 PS5000,提供了最大5G的速度和远超100G以上的测试向量能力,非常好的支持了包含Scan-Over-HSIO在内新的Scan接口技术。满足了未来Scan 测试演进的要求。”

与结构化测试主要针对的单个IP核不同的是,系统级测试针对的是芯片整体及IP核同IP核之间的交互部分,是对芯片在其应用工作模式下的测试。结构化测试虽然能在单核层面做到高缺陷覆盖率,对于复杂的芯片依然会有覆盖率的缺失。“进入2.5D/3D封装时代,保证Die是KGD(Know good die)是非常必要的。ATE设备需要增加系统级测试能力。爱德万测试在去年推出的Link Scale板卡,是业界的一款创新的测试仪器,这块板卡里面内建了完整的主控能力,通过Link Scake在ATE设备中加入面向系统级的测试功能。”

此外,葛樑介绍,爱德万测试目前也在做失效分析方面的探索。随着3D集成成为微电子封装的主流,芯片的体积越来越小,结构复杂,层数很多。面对失效的情况,快速且精准地定位问题发生在哪里十分重要,且精准度往往需要达到微米级别。这对失效分析手段提出了挑战,也对故障高分辨率定位能力的需求逐渐增大。这里Advantest TS9001 太赫兹 TDR 系统,通过发出快速的脉冲波形并抓取回波并分析来定位问题点,其分辨率达到了 5 um,达到了对2.5D/3D 封装进行问题定位的要求,已经被很多客户采用。

可以说,半导体测试始终需要随着芯片技术的不断发展而蜕变升级。而越高端、越复杂的芯片对测试的依赖度越高,同时测试设备的高级功能对于5G、IoT和云计算等半导体厂商来说变得越来越重要。

登录

登录