今天GSA全球存储峰会“构建数字未来”通过线上方式举行,钰创科技董事长、CEO兼创办人卢超群发表了题为《具有创新DRAM和AI边缘架构的智能万亿级单片式及异构集成微系统》的演讲。

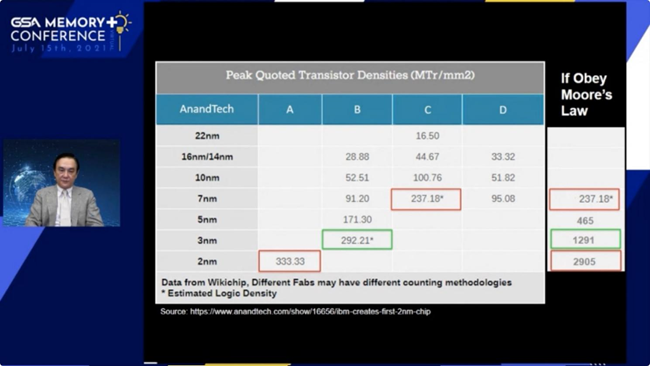

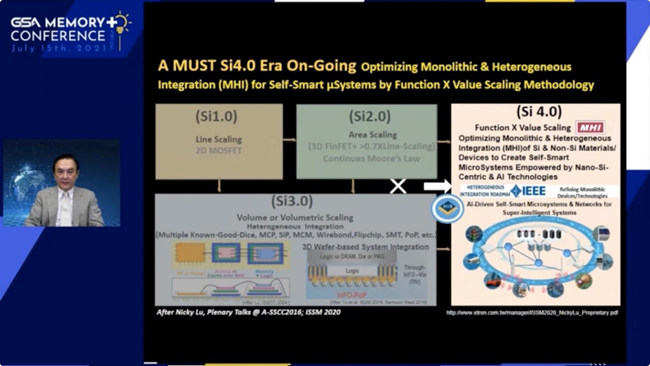

卢超群表示,在硅1.0时代,芯片尺寸缩微通过0.5微米~28nm平面工艺来实现,主要技术突破依赖三极管、材料和工艺方面的创新,包括铜金属、CMP等等;在硅2.0时代,引入了三维晶体管结构,通过FinFET工艺实现了7nm以下制程,并预计可以演进到3nm,2nm,单位面积的晶体管数量成倍数增长。但是摩尔定律也随之走到了极限。假设晶体管密度继续遵循摩尔定律,在2nm工艺时晶体管密度应该达到29.05亿个/mm2,但事实上最近IBM公司展示的2nm工艺,晶体管密度仅达到3.33亿个/mm2。因此硅3.0时代,三维立体堆叠技术对于芯片性能的继续提升起到了至关重要的作用。

在硅3.0时代,异构集成对硅工艺继续演进发挥了重要作用。它将不同工艺架构、不同指令集、不同功能的硬件组合成一个计算系统,在平面和垂直方向上实现器件尺寸缩微。台积电为苹果研发的InFO、CoWoS等封装技术随后被广泛用于数量众多的系统上,从另一个维度推动了半导体技术的发展。卢超群指出,异构集成的特点是可以融合不同的工艺、材料和器件,通过系统设计的理念、2.5D/3D高密度结构来实现高密度集成,以推动有效摩尔定律经济(EME,Effective Moore's Law economy)。

卢超群还提出了激进的演进路径并称之为硅4.0时代,即通过微小创效优化单片式和异构集成,通过硅和非硅材料、器件、系统来创建自主智能(self-smart)微系统,以纳米硅为中心和AI技术打造自智能微(self-smart)系统的材料/设备。最终目标不仅是实现几何缩放,更是以最节能的方式实现更快的系统性能、更智能的功能以及更高的业务、生产力和价值。

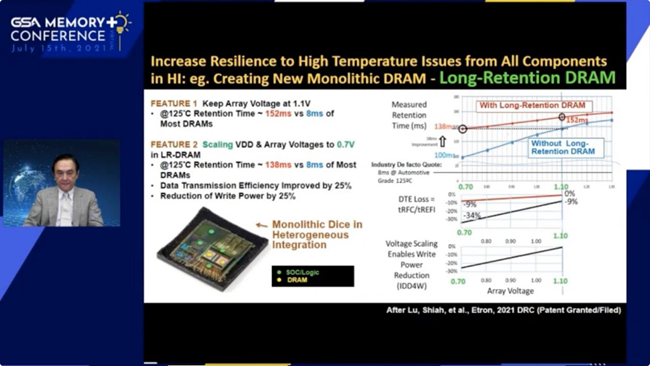

他以钰创正在进行的一些DRAM相关研发举例。在越小的外形尺寸下,越高的性能会产生越大的功耗,从而导致更高的温度。例如在生产一个单片式DRAM器件时,就需要提高其异构集成的所有组件耐高温的性能。因此,在新时代,异构集成最困难的挑战之一,就是如何减少热耗散和温升。钰创还通过RPC(减少引脚数量)、FPGA和AI等技术融合实现DRAM功能的创新。

卢超群还首次披露了与ITRI的合作项目,一个新型的为智能AI边缘子系统设计的D2-HI架构,D2指DWB+DSIP,其中还集成了一个AI芯片。基于该架构的异构集成DRAM芯片可用于多摄像头人像追踪和人脸识别系统。D2-HI架构相比传统的DDR4,MAC效率提升至83.6%,性能也提升了81%,并具有更小的尺寸和更低的功耗。

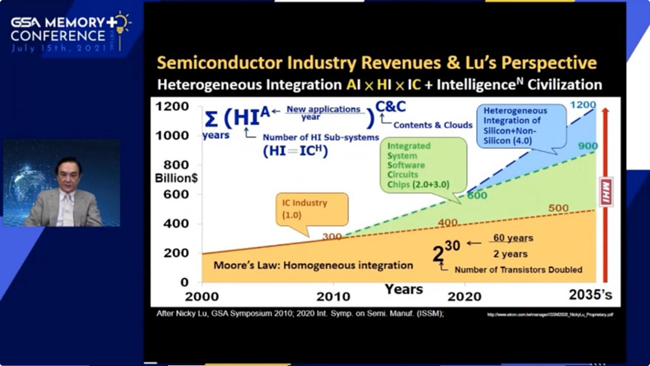

卢超群总结说,通过异构集成等技术,可以获得等效更高工艺节点的性能,从而节约了成本,获得更好的投资回报。他强调,AI、IoT时代的半导体技术,都专注于新功能的时间价值和产品价值。此外,还可以通过集成系统、软件、电路和芯片来实现超越摩尔定律的增长。AI、HI(异构)和集成电路的乘法效应,加上智能文明,将在未来为半导体产业带来数万亿美元的价值。(校对/木棉)