西安电子科技大学模拟集成电路重点实验室梁鸿志、朱樟明团队在高能效8位32GS/s高度数字化模数转换器(ADC)芯片方向取得重要进展。团队基于28nm CMOS工艺提出了一款高能效8位32GS/s混合域架构时序交织ADC芯片,针对传统时间域ADC在PVT波动下性能不稳定的问题,采用多种自适应校准机制以提升系统鲁棒性;通过提高单通道采样速率、减少交织通道数量,从源头上缓解通道失配影响,并进一步降低系统复杂度与功耗开销,适用于超大规模数据中心、云计算平台及高速串行接口系统等应用场景。相关成果发表在2026年《IEEE Journal of Solid-State Circuits》(JSSC),论文题目为" A 16× Interleaved 32-GS/s 8b Hybrid ADC With Self-Tracking Inter-Stage Gain Achieving 44.3-dB SFDR at 20.9-GHz Input"(DOI: 10.1109/JSSC.2026.3680919)。论文第一作者为西安电子科技大学梁鸿志,第一学生作者为常军,共同通讯作者为西安电子科技大学朱樟明、刘术彬、沈易、李登全。

论文链接

https://ieeexplore.ieee.org/document/11482810

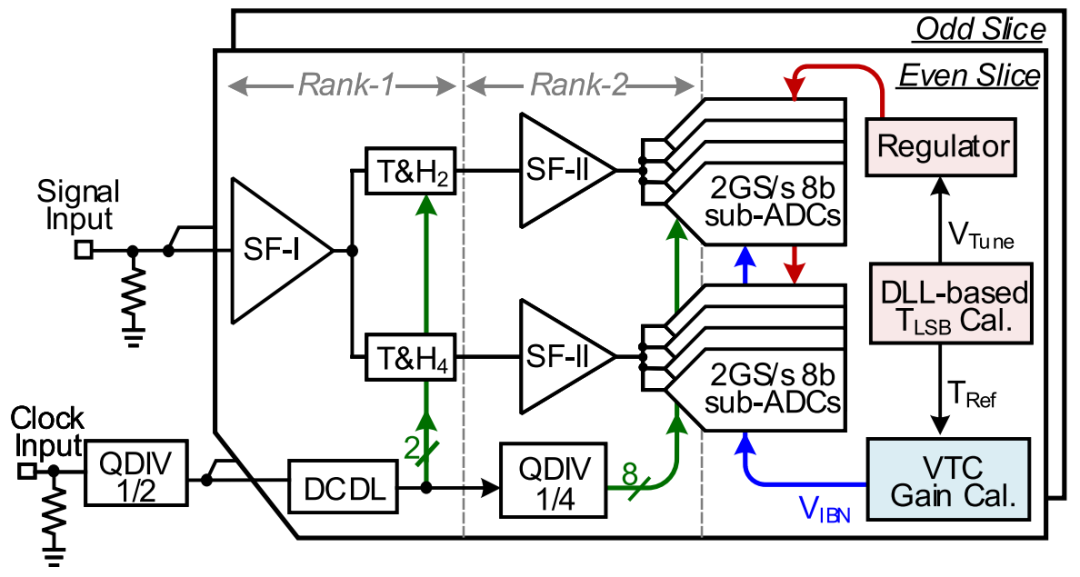

该工作提出了基于延时锁相环的量化范围自跟踪校准技术,通过构建与子ADC一致的延时复制链,实现对时间量化步长及满量程范围的实时跟踪与补偿,从根本上抑制PVT变化对系统精度的影响;引入模拟域自跟踪级间增益校准环路,通过电压-时间转换复制结构实现级间增益的自适应调节,有效解决了传统结构中级间增益失配对线性度和动态性能的制约;通过在前端引入逐次逼近辅助粗量化并嵌入失调校准机制,在降低后端时间量化精度要求的同时,实现了通道间失调误差的高效抑制,避免了复杂数字校准带来的额外硬件开销。

图1 高度数字化混合域交织ADC系统架构

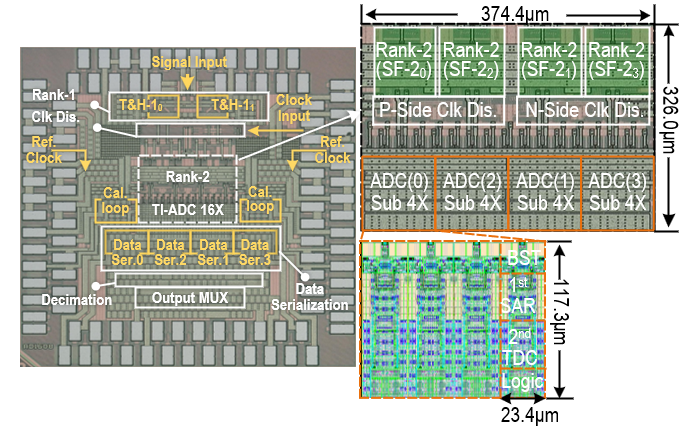

测试结果表明,该芯片在32 GS/s采样速率下,在奈奎斯特输入条件下实现了36 dB的SNDR和50.8 dB的SFDR;在20.9 GHz高频输入信号下仍保持44.3 dB的SFDR及超过5位的ENOB,展现出优异的宽带信号处理能力。本研究在大规模时间域ADC交织架构的鲁棒性优化方面提供了关键技术支撑,并为工艺演进驱动下的高可靠性高度数字化架构设计树立了新范式。

图2 芯片显微照片及面积分解

论文信息

Hongzhi Liang, Jun Chang, Yixiao Luo, Li Dang, Haolin Han, Yi Shen, Dengquan Li, Shubin Liu, Ruixue Ding, and Zhangming Zhu, "A 16× Interleaved 32-GS/s 8b Hybrid ADC With Self-Tracking Inter-Stage Gain Achieving 44.3-dB SFDR at 20.9-GHz Input," IEEE Journal of Solid-State Circuits, doi: 10.1109/JSSC.2026.3680919 (Early Access).