(文/罗叶馨梅)大日本印刷株式会社(DNP)近日宣布,成功开发出电路线宽为10nm的NIL纳米压印光刻掩膜版,可用于相当于1.4nm级逻辑半导体的电路图形化。公司表示,该产品面向智能手机、数据中心、NAND闪存等应用场景中尖端逻辑芯片的微型化需求,目前已启动客户评估工作,计划于2027年实现量产。DNP同时提出,力争在2030财年将纳米压印相关业务销售额提升至40亿日元。

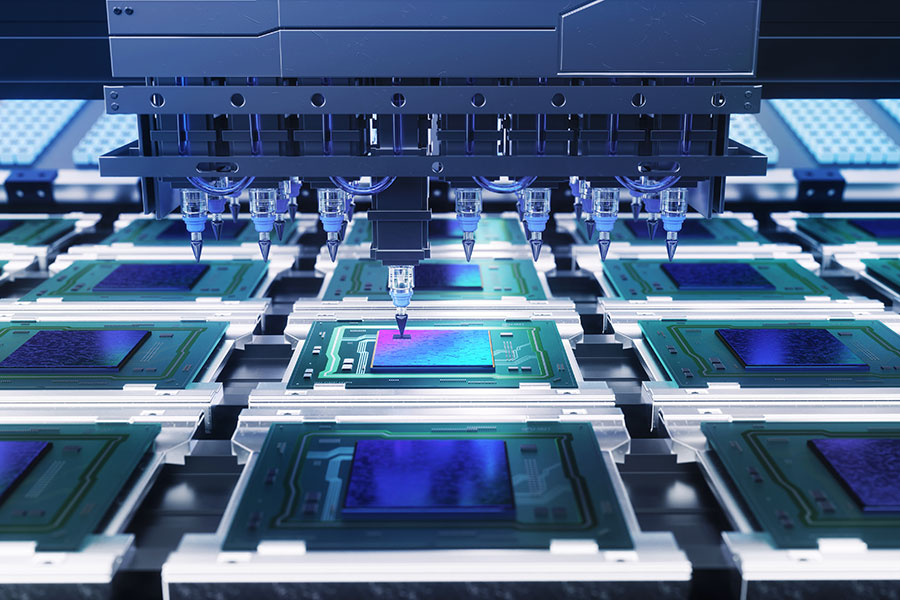

DNP指出,随着终端设备性能持续提升,市场对更先进制程逻辑半导体的需求不断加大,推动基于极紫外(EUV)光刻的生产技术演进。但EUV在生产线建设和曝光过程中需要巨额资本支出及高能耗,制造成本与环境负担成为行业关注焦点。自2003年起,DNP持续研发纳米压印光刻掩膜版,通过将电路图形直接压印到基板材料上,为制造商在部分工艺环节降低曝光能耗、优化成本结构提供了新的技术路径。

此次推出的10nm线宽NIL纳米压印光刻掩膜版,可在部分图形化环节替代EUV光刻,为尚未导入EUV生产线的半导体制造商提供先进逻辑制程选项。DNP表示,通过向客户供应该光刻掩膜版,有望在保持图形精度和线宽控制的前提下,扩大先进制程图形化的工艺选择空间,协助客户在制造成本和环境负担之间取得平衡。公司认为,随着逻辑器件持续向更精细线宽演进,纳米压印工艺在部分节点可能具备一定经济性优势。

在具体工艺技术上,DNP引入自对准双重成像(SADP)技术,对光刻形成的图形进行薄膜沉积和蚀刻,使图形密度实现翻倍,在此基础上实现10nm线宽的纳米压印光刻掩膜版。公司称,本次研发不仅利用了其在光掩模制造领域长期积累的高精度图形化能力,还结合了晶圆制造工艺技术,从而在产品精度、稳定性与可量产性方面满足先进逻辑半导体的要求。根据公司测算,基于纳米压印的超细半导体节能加工技术,可将曝光环节的能源消耗降至当前主流制程的大约十分之一。

在产业化推进方面,DNP已与半导体制造商开展沟通,并启动新型NIL纳米压印光刻掩膜版的评估工作。公司计划在完成客户验证、建立量产工艺和供应体系后,于2027年开启量产供货,以应对逻辑半导体微缩带来的新增需求。DNP表示,将持续推动纳米压印光刻掩膜版技术升级和产能扩充,以匹配未来市场放量节奏,将相关业务培育为公司半导体板块的重要增长点。

此外,DNP计划在2025年12月17日至19日于东京国际展览中心举办的SEMICON Japan 2025上展出这款10nm线宽NIL纳米压印光刻掩膜版。公司认为,通过在专业展会集中展示产品与技术路线,可加深与全球半导体制造企业及设备厂商的交流,推动纳米压印工艺在先进逻辑制程中的应用探索。后续该技术在量产良率、生产节拍以及与既有工艺整合方面的表现,将成为市场持续关注的重点。

(校对/秋贤)