2024年10月27日-31日,国际计算机辅助设计会议(IEEE/ACM International Conference on Computer-Aided Design,ICCAD2024)于美国新泽西州召开。ICCAD是EDA领域的国际顶级学术会议,自1982年创办以来,迄今已经举办了42届,与DAC、DATE和ASP-DAC并称为EDA领域四大国际顶级学术会议。

今年,ICCAD共收到810余篇论文投稿,中稿率约24%。经过遴选,本次ICCAD最终分别从面向集成电路设计中前端和后端过程的研究论文中评选出1篇论文授予最佳论文奖。其中信电学院师生发表的论文《一种面向大模型高效加速器设计和模型推断的敏捷框架》获得本次会议的最佳论文奖(前端)。该工作的作者包括信电学院硕士研究生陈律丞、博士研究生吴莹、温晨怡等,这是中国内地高校机构首次以第一单位获得ICCAD最佳论文奖。

迄今为止,信电学院师生在EDA领域四大顶会上硕果累累,共计获得了3次最佳论文奖、2次最佳论文提名奖(仅统计第一单位为浙大的论文)。

以下是ICCAD2024最佳论文奖论文介绍:

大语言模型(Large Language Model, LLM)凭借大规模训练数据、庞大的模型参数量和计算开销,涌现出了强大的生成能力、泛化能力和交互能力,在各个领域展现出了非凡的性能,拉开了“人工智能生成内容”(AIGC)时代的序幕。然而,大模型中往往包含着几十到几千亿的参数,所带来的海量矩阵和向量浮点乘法操作需要大量的计算资源,这些都成为了模型推理的关键瓶颈。为了跟上模型发展的步伐,设计者需要频繁修改优化芯片架构,开发流程繁琐冗长,需要经历多轮次的迭代才能完成芯片的最终定型并交付流片。对于复杂的大模型任务带来的新挑战,如何实现大模型芯片的敏捷开发与高效计算是当前各界亟待解决的关键问题。

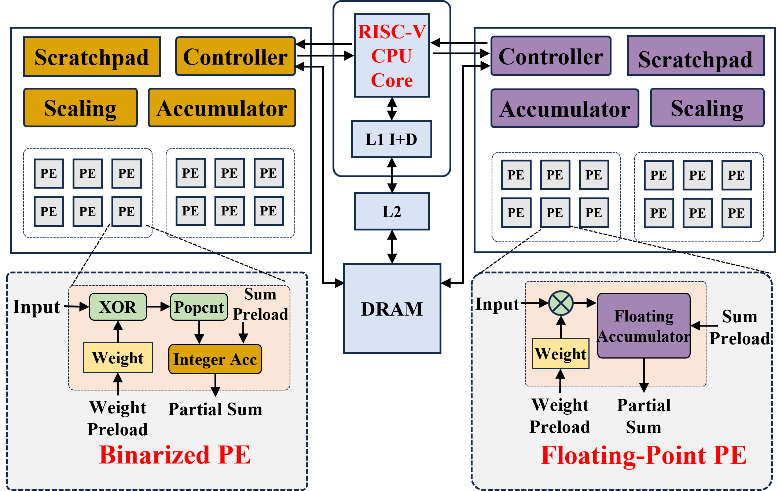

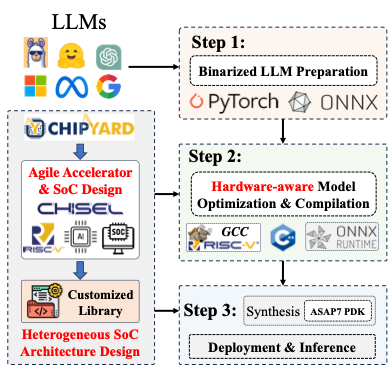

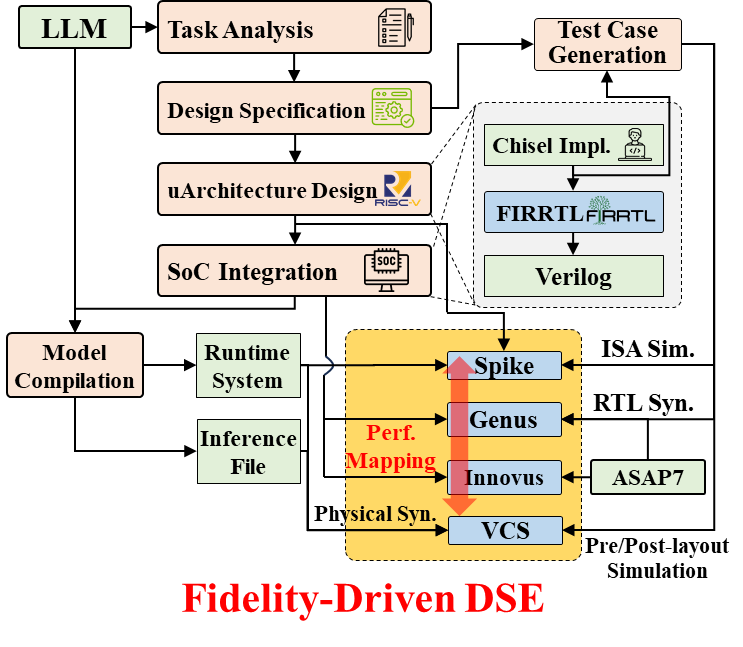

针对这些问题,团队提出了一个大模型高效推理加速器开发和敏捷优化框架。首先,团队提出了一种二值化大模型脉动阵列加速器,并实现了一个基于RISC-V CPU、同时支持二进制和浮点运算的异构SoC。通过将大模型进行二值化压缩,可以将高位宽、高精度的数据按组转为低位宽、低精度的数据(最多可以将矩阵模块的存储压缩64倍),依靠二进制运算代替传统浮点运算,实现了快速乘法计算,极大降低了模型参数存储和计算开销。所提出的异构SoC同时可以兼容高精度浮点计算以确保模型推理精度。在框架中,团队还提出了一种基于多保真度优化的敏捷设计空间探索方法,通过跨EDA多个阶段的协同建模与优化,解决了传统机器学习方法因缺乏准确的性能数据而出现的过拟合问题,可以在芯片设计的早期阶段完成对芯片性能、功耗的快速精确评估。通过结合贝叶斯优化等设计空间探索算法,在芯片设计早期完成设计优化与决策,避免了后期极为耗时的仿真流程,极大提高了开发、优化效率和设计质量。

图1 大模型异构SoC架构

图2 团队提出的开发框架与面向大模型SoC的敏捷开发流程

本框架涵盖了大模型二值化、架构设计、模型编译、芯片综合优化与模型推理,实现了端到端的敏捷优化。在LLaMA-7B、OPT等代表性大模型上,相比当前流行的CPU/GPU计算设备,在获得11.7倍推理加速的同时可将能耗效率提升2.19倍,并显著降低了芯片开发成本,实现了超过3个数量级的效率提升,极大助力了大模型时代我国集成电路设计技术的发展。