随着 2 纳米工艺节点的临近,一些障碍正在出现,可能会进一步阻碍本已缓慢的摩尔定律进程。其中一个挑战是如何在不影响性能提升的情况下,利用铜线为数百亿个微小晶体管有效分配电能。现在,半导体制造设备的主要供应商应用材料公司(Applied Materials)相信已经找到了答案。

上周,应用材料公司揭开了其最新材料工程解决方案的神秘面纱,这些解决方案旨在使铜布线的尺寸缩小到 2 纳米及以下,同时降低电阻并增强芯片的三维堆叠能力。

该公司的 Black Diamond 低介电材料从 2000 年代初就开始供应。这种材料在铜线周围形成一层特殊的薄膜,可减少电荷的积聚,而电荷的积聚会增加功耗并造成电信号之间的干扰。

现在,应用材料公司推出了增强版Black Diamond,进一步降低了最小 K 值,从而使铜布线扩展到 2 纳米节点,同时还提高了机械强度--这是芯片制造商希望垂直堆叠多个逻辑和内存芯片时的一项关键性能。

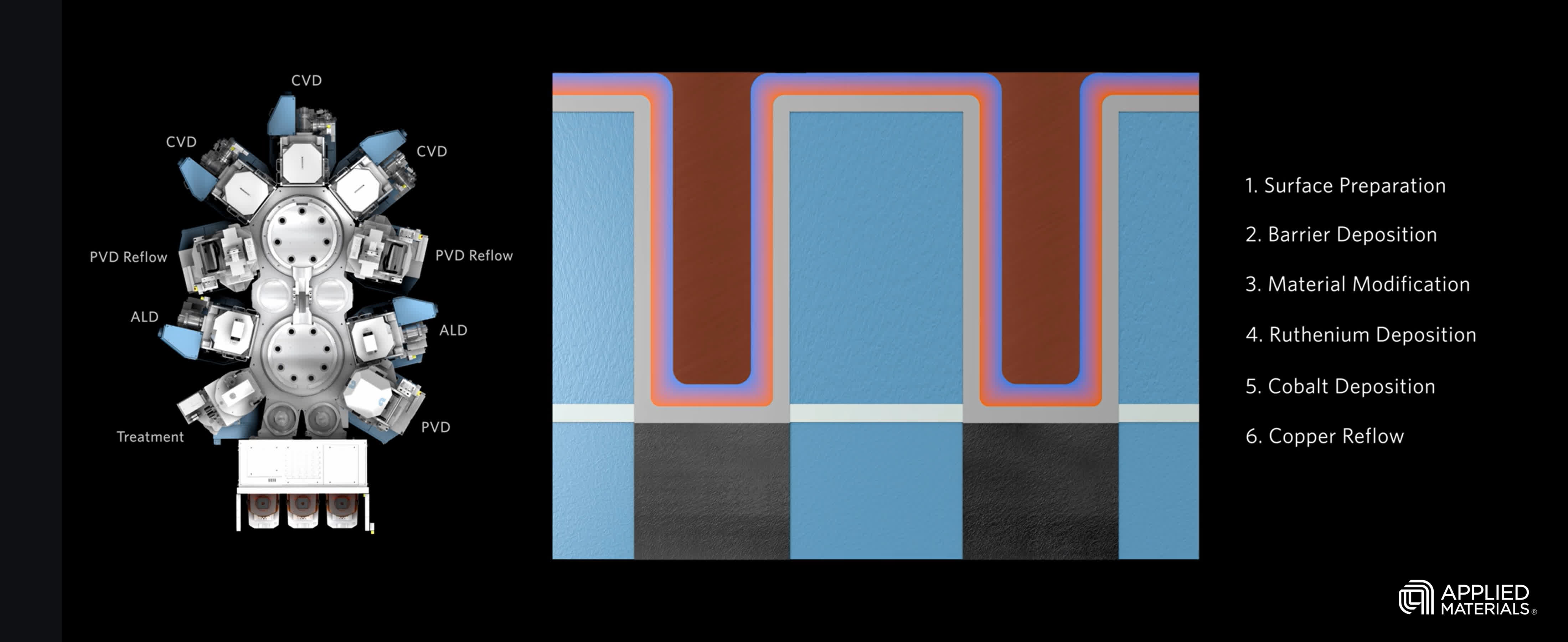

但是,随着尺寸的缩小,铜线本身的缩放是另一个巨大的挑战。如今,最先进的逻辑芯片可容纳超过 60 英里长的铜线,首先要在介电材料上蚀刻出沟槽,然后沉积一层超薄阻挡层,以防止铜线迁移。在最后的铜沉积填满剩余空间之前,还要沉积一层衬垫层,以帮助铜的附着。

问题在于,在 2nm 及以下尺寸时,阻挡层和衬垫层消耗的可用沟槽体积比例越来越大,几乎没有足够的空间来填充铜,并有可能产生高电阻和可靠性问题。应用材料公司利用这种全新的材料组合解决了这一难题。

他们最新的集成材料解决方案(IMS)将六种不同的核心技术整合到一个高真空系统中,包括业界首创的钌和钴配对技术,以形成超薄的 2 纳米二元金属衬垫。与前几代产品相比,衬垫厚度减少了 33%,同时还改善了表面性能,实现了无缝、无空隙的铜粘附和回流。最终,芯片布线中的电阻降低了 25%,从而提高了性能并减少了功率泄漏。

应用材料公司称,所有领先的逻辑芯片制造商都已采用其新型铜阻挡层种子 IMS 与钌 CVD 技术生产 3 纳米芯片,预计 2 纳米节点也将采用这种技术。

该公司还估计,随着背面功率传输方案的引入,其芯片布线解决方案的服务可用市场总额将从现在的每 10 万片晶圆约 60 亿美元激增到 70 多亿美元。