近日,集微网获悉上海易卜半导体有限公司在自有专利基础上,成功开发出国内首创,具有行业领先水平的新型Chiplet封装技术。为一探究竟,集微网专程走访了位于上海宝山区机器人产业园的易卜半导体总部,第一时间进行了独家采访。

易卜半导体副总李文启博士表示,这次易卜半导体推出Chiplet封装新技术不是一蹴而就,而是一个长期积累厚积薄发的过程。创始团队从2019年开始便高度关注集成电路技术发展趋势,深刻认识到随着摩尔定律的放缓,先进封装的重要性将与日俱增。在后摩尔时代,芯片的特征尺寸已接近物理极限,其复杂度和开发制造成本已成为芯片继续提高性能和良品率的制约因素,而先进封装技术把多颗芯片异构集成在一个高密度封装体内是进一步提高芯片性能的必由之路。

“易卜半导体成立伊始,便全力投入多芯片集成封装技术的研发,特别是针对封装设计和制造的痛点和难点提出和开发了一系列解决方案,在封装技术主要国家和地区申请了110多项发明专利,其中45项发明专利已获授权,基本完成了先进封装领域核心知识产权的战略布局。”李文启博士表示,“易卜这次推出的两项突破性2.5D Chiplet封装技术COORS-R和COORS-V正是基于其中的几项自有核心专利,在自有的研发和生产线上开发成功的,拥有全部知识产权。”

据悉,易卜半导体的几项先进封装核心专利技术经权威第三方科技评审机构评估,认为“多项设计和工艺技术指标达到国内领先,国际先进水平,填补了国内空白”。李文启博士指出,目前国内先进封装产业整体上还处于初期发展阶段,以跟随和模仿为主,努力追赶国际水平。但在当前国际科技竞争越来越激烈,大模型人工智能发展一日千里的大背景下,国内高算力芯片企业对先进封装技术特别是2.5D Chiplet封装技术都有迫切需求。易卜推出的COORS-R和COOR-V两项封装技术可谓应运而生,应时而至,为高算力芯片提供了从封装设计、仿真、开发到量产的一站式服务解决方案。

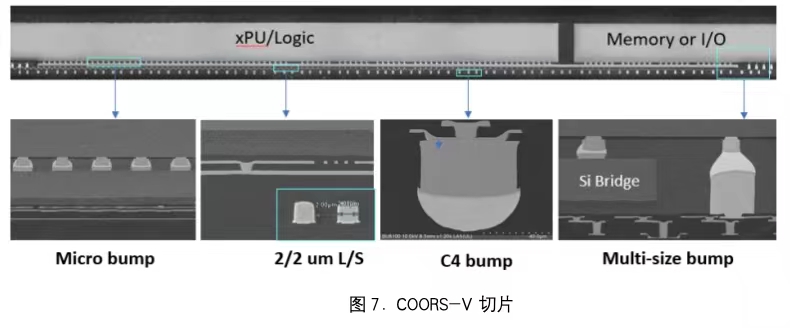

易卜半导体工程总监靳春阳进一步介绍,易卜的COORS-R属于RDL-First类型的Chiplet封装,而COORS-V则是在COORS-R基础上加入硅桥设计,进一步提高封装集成度。这两项技术在芯片互连密度和封装效率上均已达到业界一流水平,而制造成本与基于硅转接板(Si Interposer)的主流封装技术相比则有大幅改善。COORS-V中的硅桥尺寸比硅转接板大幅减小,也不用硅通孔(Through Silicon Via,TSV)工艺,易于加工,在成本和可生产性方面具有显著优势。

关于COORS-R和COORS-V技术的应用,李文启博士提到,这两种先进封装技术可用于不同种类不同功能的多芯片异质集成。目前最主要的应用领域是在xPU (GPU, CPU, DPU…)和存储器(HBM,DDR,LPDDR…)之间的高密度短距离高带宽互连,以提高xPU和存储器之间的通信带宽,实现近存计算。目前设计的COORS-V可支持两颗xPU SoC芯片、 4颗HBM3或者HBM3E和4颗硅桥芯片集成封装,带宽分别达到3276.8GB/s和4710.4GB/s,可满足当前多数高算力芯片的设计要求。

“我们正在和一些Chiplet客户进行协同设计和技术对接。”李文启博士还透露,下一代COORS-V已进入设计和开发阶段,有望在今年底完成开发并推向量产,届时Chiplet芯片性能和互连带宽会有进一步提升。

记者进一步了解到,易卜半导体拥有经验丰富的业界一流的研发和工程团队,采用了行业中最先进的信息管理系统,并获得ISO9001、 ISO14001和ISO45001认证。除了Chiplet先进封装,易卜的生产线也具备成熟的Bumping、WLCSP和Fan-out等晶圆级封装规模量产能力,同时也为客户提供晶圆测试服务(CP Test)。当前,易卜半导体在深耕现有量产客户的同时,正全力支持多家客户进行产品认证。离开易卜半导体前,记者有机会参观了易卜的生产工厂,亲身感受到了繁忙而有序的产线环境和工作氛围。