(文/陈炳欣)国际固态电路会议(ISSCC)是展示固态电路和片上系统进展的全球性学术会议,每年都会吸引超过3000名来自世界各地工业界和学术界的参加者。本届ISSCC 2024的整个会议议程包括了10个教程、6场高级电路设计论坛,以及数量众多的技术论文展示、特别活动,涵盖大型语言模型的节能AI计算系统、数字增强模拟电路、智能传感、高性能频率合成电路和系统、高度集成的电光收发器等,很多议题反映了当前集成电路领域的技术热点。引人关注的是,本届会议上来自中国(包括内地、香港、澳门)的论文数量上再次蝉联第一,显示国内集成电路领域在技术研究上取得了阶段性成绩。但是,成果主要集中在模拟、电源等小芯片方面,在先进处理器、AI大芯片等方面,仍然差距较大,国内还需要继续保持学习。

光电融合:为高性能计算系统设计开辟新途径

光电融合的发展趋势在今年的ISSCC会议得到了充分体现,在台积电资深副总经理张晓强应邀做的第一个开场主旨报告《Semiconductor Industry: Present & Future半导体产业:现在和未来》中便多次谈到,硅光电子技术在未来高性能计算中的重要作用。

张晓强博士指出,目前在高性能计算领域普遍采用电子技术进行信号传输,但是系统功耗很高,随着未来需要更高速的信号传输与更高的带宽,这就需要在封装中将电子转换为光子,使用共封装光学的先进封装技术把光子能力引入芯片当中。CPO全称共封装光学(Co-Packaged Optics),其形态上将光引擎封装至离交换机ASIC很近的地方,从而减少电链路(ASIC-光引擎)的距离,可大幅减少射频传输损耗,提高信号带宽。

张晓强博士强调,结合先进的堆叠技术,将硅基光电子技术与电子芯片技术结合起来,是未来发展的关键方向。通过这种结合,可以显著降低功耗(减少至50%)并提高效率,达到5pJ/bit的能耗。这显示出硅基光电子技术在未来半导体技术中的潜力和重要性。

张晓强还指出,将硅基光电子技术引入封装中,不仅能够提高数据处理和传输的效率,还能够通过在封装中集成电压调节器,利用硅基光电子技术来解决电力传递和互连密度的问题,从而为高性能计算设备提供更高的能效和性能。

除此之外,本届ISSCC2024上有关光电融合的议题还有很多。比如,Ghent University - IMEC的Gunther Roelkens介绍了一种创新的制造技术——微转印,可用于创建异构电子-光子集成电路。这种方法允许精确地将光子设备放置在电子电路上,实现光学和电子在微观尺度上的无缝集成。这项技术对于开发紧凑、能源高效的系统非常重要,这些系统将电子的高速数据处理能力与光子学的高带宽、低延迟通信优势结合起来。

UC Berkeley的Vladimir Stojanovic探讨了在单一片上系统(SoC)平台上集成电子和光子组件的方法。这种方法将推进执行计算、通信、感知功能的SoC开发,提升效率和速度。电子和光子在SoC内的协同作用为高性能计算系统的设计开辟新途径,应用于自动驾驶汽车、数据中心、人工智能和物联网。Ayar Labs 的Chen Sun发表了硅基光电子技术在提升芯片间通信能力方面的进展,重点强调开发连接和光输入/输出芯片组,这对于提高半导体技术中的数据传输速率和效率非常重要。

ISSCC 2024对于硅基光电子相关主题的关注明确反映了当前的一个重要技术趋势,即电子芯片技术和硅基光电子技术的融合,这一趋势受到数据通信系统需求的驱动,同时也反映了硅基光电子技术在革新半导体行业方面的潜力。

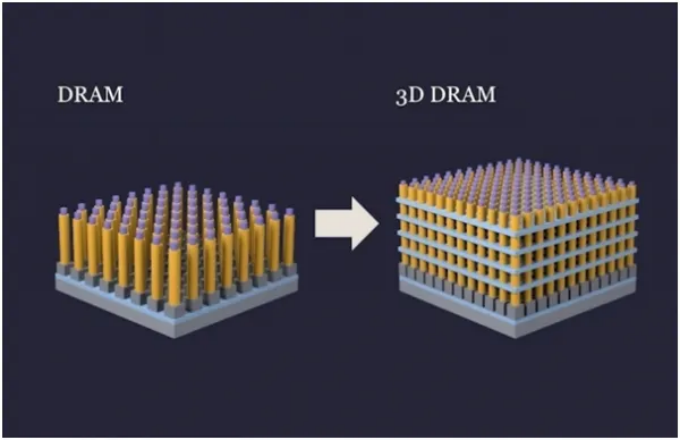

存储芯片:聚焦3D闪存和DRAM更高密度更快传输

存储一直是ISSCC研讨的重点领域,本届ISSCC在存储领域仍然以3D闪存和DRAM为主。在QLC产品领域,三星分享一篇题为《A 280-Layer 1Tb 4b/cell 3D-NAND Flash Memory with a 28.5Gb/mm2 Areal Density and a 3.2GB/s High-Speed IO Rate》的演讲,展示了280层QLC三维闪存技术,存储密度达到28.5Gb/mm2,远高于海力士321层TLC三维闪存(>20.0 Gb/mm2)和英特尔192层PLC三维闪存(23.3 Gb/mm2)。存储密度的提升得益于共享电路方案的提出,外围电路占用面积显著降低。

为了实现QLC产品传输速度的突破,三星提出方案最大传输速率可达 3.2 GB/s,显著高于现有2.4 Gb/s的QLC产品。280层QLC三维闪存只是三星QLC路线图的近期的重要一步。随着未来技术代的持续升级,QLC产品在三维存储闪存中的占比不断增加,最终性能可以与当今主流的TLC产品直接竞争,进入移动端,取代部分TLC产品市场。

在TLC领域,美光分享一篇题为《A 1-Tb Density 3-b/Cell 3D NAND Flash on a 2YY- Tier Technology with a 300-MB/s Write Throughput》的演讲,展示了2YY层TLC三维闪存技术。存储密度达到>20Gb/mm2,可以比拟海力士321层三维闪存。美光提出了编程算法、页缓冲器定序器加速和峰值功率管理等一系列性能提升方案,实现芯片功耗和传输速率的提升,最大传输速率可达 3.6 GB/s,最高吞吐量达到300MB/s,性能优于海力士321层三维闪存。可以想见,未来TLC三维闪存芯片性能进入更高性能时代。

在DRAM领域,三星在一篇名为《在第五代10纳米DRAM工艺中采用对称马赛克架构(Symmetric-Mosaic)的32-Gb 8.0-Gb/s/pin DDR5 SDRAM 》继续推动 DDR5 性能的进步。三星的目标是通过其新提出的架构将DRAM容量提高一倍。

目前,最高容量的DDR5内存采用基于16 Gb裸片并采用10纳米工艺制造的3D堆叠架构。随着终端产品中采用128Gb模块的需求不断增加,三星在论文中描述了一款单片32 Gb高密度DDR5裸片,仍采用 10 纳米工艺。三星称,基于32 Gb裸片的3D堆叠系统将提高性能,在8个芯片堆栈中使用时可支持高达1TB的内存,并实现每个引脚每秒8 Gb的速度。

三星表示,“马赛克”架构分区可以克服传统DRAM大小限制,可以在不改变整体外形尺寸或减少芯片蚀刻几何尺寸的情况下,大幅提高DRAM容量。根据三星的测算,基于32 GB的 0.5 TB DIMM比基于 16 GB 的DIMM功耗低30%,使其成为数据中心和其他容量和功耗要求较高的计算应用的理想选择。

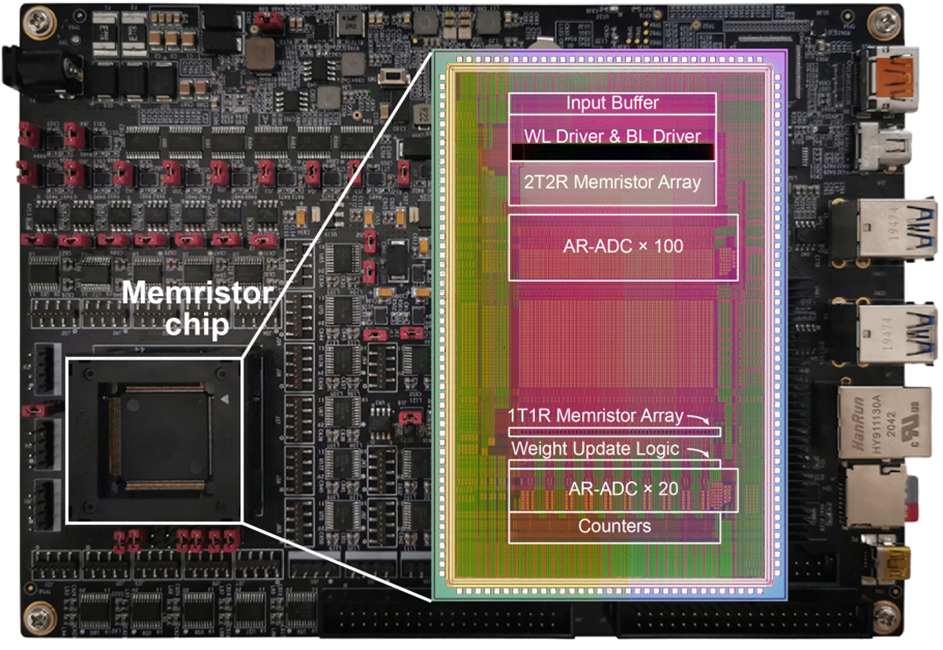

AI与存算一体:寻求计算架构上的突破

本届ISSCC2024上,关于针对人工智能高算力芯片计算架构的研究颇具活力。大语言模型的训练和推理所产生的巨大算力和能耗成为AI计算的主要限制。ISSCC2024上对此进行了大量有关高性能计算的当前和下一代电路、架构和系统的讨论,以解决与大语言模型相关的算力和能效挑战,包括GPU和HPC系统、云服务器SoC、加速器、高带宽存储访问、封装内高带宽内存和内存中的DRAM 处理等。

其中,机器学习加速器和存算一体的研究值得关注。机器学习加速器和CIM架构位于启用AI和ML工作负载的前沿,ISSCC 2024对这些领域给予显著关注。随着AI应用在复杂性和普遍性上的增长,对专门硬件的需求日益迫切,这些硬件能够以能源高效的方式提供高计算功率。关于ML硬件的会议重点则放在支持神经网络模型的扩展和AI算法的高效执行的架构创新和设计策略上,强调硬件软件协同设计的重要性以及内存计算在革新AI处理中的潜力。

由于存算一体出色的能效比和计算速度,其正在成为取代通用GPU执行人工智能计算的最佳选择。目前,国内的高校如清华大学、北京大学等均在积极推进存算一体架构的研究与发展。在本届ISSCC会议上展示了许多研究成果,预示着中国未来凭借存算一体技术有望实现技术上的超越。

中国研发:先进处理器、AI大芯片差距依然明显

中国(包括内地、香港、澳门)今年入选ISSCC的论文数量继续蝉联第一,达到69篇(全球为234篇),相较于去年从ISSCC 2023的入选论文数量进一步增加。具体发表情况为,澳门大学 14篇,清华大学13篇,东南大学6篇,北京大学5篇,中科大5篇,南科大5篇,电子科大4篇,复旦大学3篇,浙江大学2篇,港中大(深圳)2篇,中国科学院微电子所2篇,中国科学院半导体所1篇,西安交大1篇,华东师范1篇,上海交大1篇,中山大学1篇,北京理工大学1篇,同济大学1篇,万高科技(杭州)1篇。

这首先表明国内在集成电路设计方面的学术研究水平快速提升,我国在芯片设计创新能力方面得到长足进步。但是依然需要看到,国内成果更多地属于学术导向的研究,应用和需求牵引导向的研究成果仍然较少,这就导致研究成果与产业应用之间存在很大的鸿沟。而美国方面,虽然目前在文章数量上少于我国,但是有大量的巨头芯片公司所主导的成果被发表。在产业需求主导的成果上,我国差距依然很大。此外,还应注意到的是,单纯从文章数量方面我国取得了领先,但是主要集中在模拟、电源等小芯片方面,在先进处理器、AI大芯片等方面,我们仍然差距较大。

当然,同样是一篇成果,大芯片所需要的研发资源、资金、流片工艺水平、团队规模等方面都要比小芯片要复杂得多,高校团队很难在这些方面与国际巨头芯片企业相抗衡。因此,无论是企业还是高校,依然要清醒认识到差距,对未来前行的困难要做好充分的心理准备,才能更好更快地追赶上国际先进水平。