集微网消息,日本佳能公司10月13日宣布推出FPA-1200NZ2C纳米压印(NIL)半导体制造设备。佳能CEO Fujio Mitarai曾表示,该公司的新纳米压印技术将为小型半导体制造商生产先进芯片开辟一条道路,目前这种技术几乎完全属于该行业最大的公司。

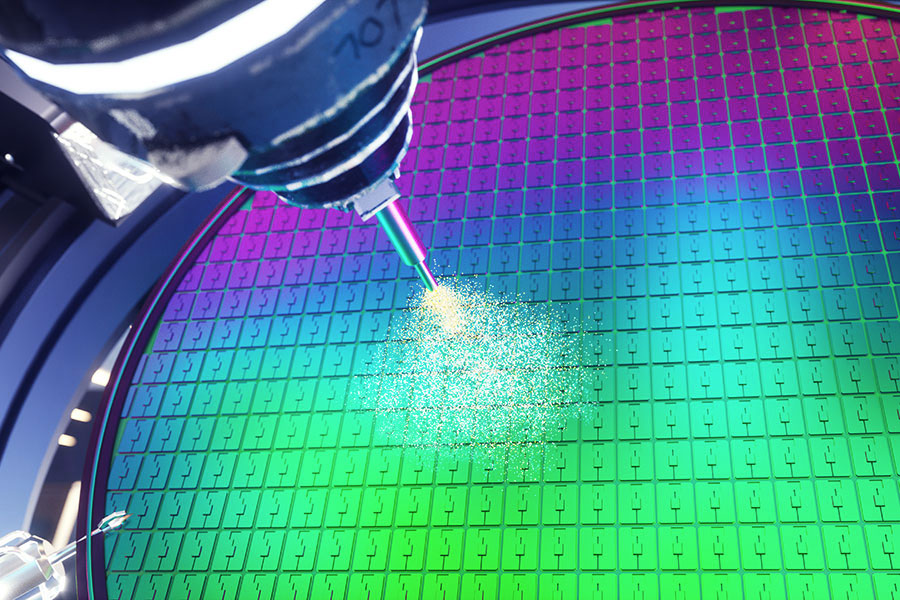

在解释纳米压印技术时,佳能半导体设备业务部长岩本和德(Iwamoto Kazunori)表示,纳米压印技术就是把刻有半导体电路图的掩模压印到晶圆上。在晶圆上只压印1次,就可以在合适的位置形成复杂的二维或三维电路。如果改进掩模,甚至可以生产电路线宽为2nm的产品。目前,佳能的NIL技术使图案的最小线宽对应5nm节点逻辑半导体。

据悉,5nm芯片制造设备行业由ASML主导,佳能的纳米压印方法或将有助于其缩小差距。

在设备成本方面,岩本和德表示,客户的成本因条件而异,据估算1次光刻工序需要的成本有时降至传统光刻设备的一半。纳米压印设备的规模减小,在研发等用途方面也方便引进。佳能CEO Fujio Mitarai曾表示,该公司的纳米压印设备产品的价格将比ASML的EUV(极紫外线)设备低一位数,不过最终的定价决定还没有做出。

据悉,在客户方面,佳能目前收到了半导体厂商、大学、研究所的很多咨询,作为EUV设备的替代产品,纳米压印设备备受期待。该设备可用于闪存、个人电脑用DRAM及逻辑等多种半导体用途。

(校对/孙乐)

登录

登录