随着信息数据大爆炸时代的来临,市场对存储器的需求持续增长。在芯片成品制造环节中,市场对于传统打线封装的依赖仍居高不下。市场对于使用多芯片堆叠技术、来实现同尺寸器件中的高存储密度的需求也日益增长。这类需求给半导体封装工艺带来的不仅仅是工艺能力上的挑战,也对工艺的管控能力提出了更高的要求。

在这里,我们将向大家介绍长电科技的多芯片堆叠封装技术的优势、工艺和管控能力,内容将分为上下两期呈现。

多芯片堆叠封装技术优势

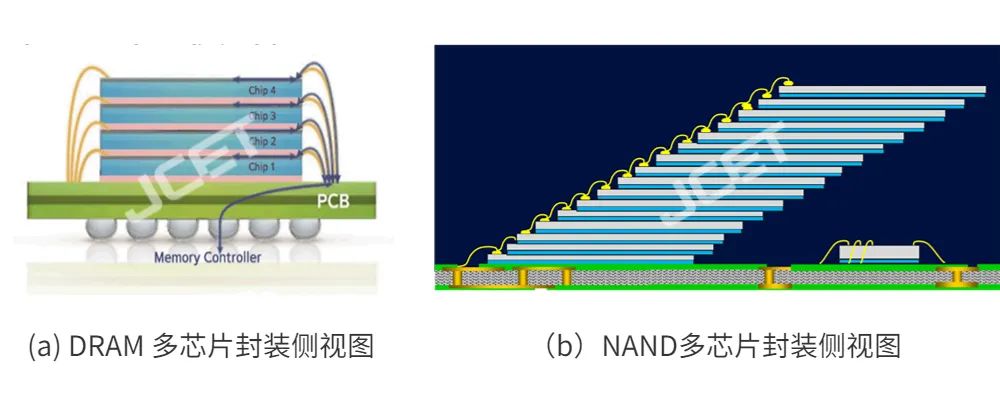

图1 多芯片封装侧视图

图1是两个不同类型的存储器封装的侧视图,从其封装结构我们可以看出,两个封装都是由多个芯片堆叠而成,目的是为了减少多芯片封装占用的空间,从而实现存储器件尺寸的最小化。其中较关键的工艺是芯片减薄、切割,以及芯片贴合。

从市场需求来看,倒装封装(FC)和硅通孔(TSV),以及晶圆级(wafer level)的封装形式可以有效地减小器件尺寸的同时,提高数据传输速度,降低信号干扰可能。但就目前的消费类市场需求来看,还是基于传统打线的封装形式仍占较大比重,其优势在于成本的竞争力和技术的成熟度。

长电科技目前的工艺能力可以实现16层芯片的堆叠,单层芯片厚度仅为35um,封装厚度为1mm左右。

多芯片堆叠封装关键工艺之芯片减薄、切割

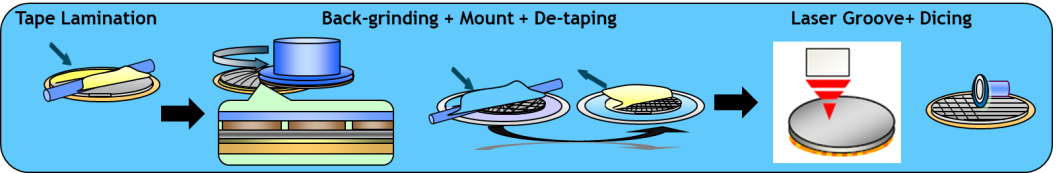

研磨后切割

(Dicing After Grinding,DAG)

主要针对较厚的芯片(厚度需求>60um),属于较传统的封装工艺,成熟稳定。晶圆在贴上保护膜后进行减薄作业,再使用刀片切割将芯片分开。适用于大多数的封装。

图2 DAG(来源:DISCO)

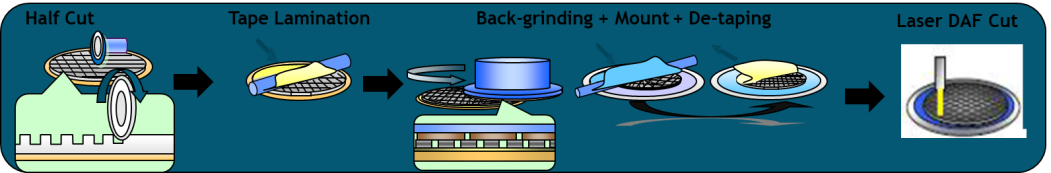

研磨前切割

(Dicing Before Grinding,DBG)

主要针对38-85um芯片厚度,且芯片电路层厚度>7um,针对较薄芯片的需求和存储芯片日益增长的电路层数(目前普遍的3D NAND层数在112层以上)。使用刀片先将芯片半切,再进行减薄,激光将芯片载膜 (Die attach film)切透。适用于大部分NAND 芯片,优势在于可以解决超薄芯片的侧边崩边控制以及后工序芯片隐裂(die crack)的问题,大大提高了多芯片封装的可行性和可量产性。

图3 DBG(来源:DISCO)

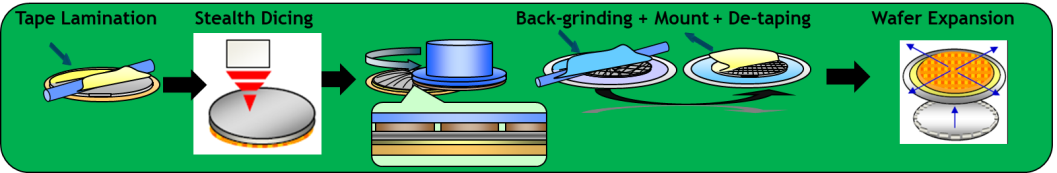

研磨前的隐形切割

(Stealth Dicing Before Grinding,SDBG)

主要针对35-85um芯片厚度,且芯片电路层厚度<7um,主要针对较薄芯片的需求且电路层较少,如DRAM。使用隐形激光先将芯片中间分开,再进行减薄,最后将wafer崩开。适用于大部分DRAM wafer以及电路层较少的芯片,与DBG相比,由于没有刀片切割机械影响,侧边崩边控制更佳。芯片厚度可以进一步降低。

图4 SDBG(来源:DISCO)

近年来,长电科技坚持创新,在先进封装技术领域厚积薄发,不断夯实在行业内的领导地位。就多芯片堆叠封装技术关键工艺而言,除了芯片减薄、切割,还有哪些?多芯片堆叠工艺如何管控?

敬请期待下期文章:

多芯片堆叠封装技术(下)

关于长电科技

长电科技是全球领先的集成电路制造和技术服务提供商,提供全方位的芯片成品制造一站式服务,包括集成电路的系统集成、设计仿真、技术开发、产品认证、晶圆中测、晶圆级中道封装测试、系统级封装测试、芯片成品测试并可向世界各地的半导体客户提供直运服务。

通过高集成度的晶圆级(WLP)、2.5D/3D、系统级(SiP)封装技术和高性能的倒装芯片和引线互联封装技术,长电科技的产品、服务和技术涵盖了主流集成电路系统应用,包括网络通讯、移动终端、高性能计算、车载电子、大数据存储、人工智能与物联网、工业智造等领域。长电科技在全球拥有23,000多名员工,在中国、韩国和新加坡设有六大生产基地和两大研发中心,在20多个国家和地区设有业务机构,可与全球客户进行紧密的技术合作并提供高效的产业链支持。

有关更多信息,请访问 www.jcetglobal.com。

登录

登录