UCIe联盟的成立再次让Chiplet成为热点。有半导体产业链中的头部玩家背书,Chiplet有望在未来改写产业的技术走向和商业发展模式。

先进封装是Chiplet实现过程中的重要一环,决定着芯片的最终成败,但是该技术的风头似乎都被晶圆厂所抢占了。那么,在Chiplet标准的大潮中,独立封装企业到底在扮演什么角色,而大陆封装业又应该以怎样的姿态去迎接标准化时代的到来呢?

先进封装强则Chiplet强

Chiplet概念并非凭空而来,源自于1970年代诞生的多芯片模组,即由多个同质或异质等较小的芯片组成大芯片。当单芯片工艺进展放缓时,Chiplet便承担了实现平衡芯片功能和生产成本的责任。

在Chiplet走红之前,一种相似的技术已经开始流行,那就是SiP(System in Package,系统级封装)。SiP的定义是将多个具有不同功能的有源电子器件与无源器件,以及诸如MEMS或光学器件等组装到一起,实现一定功能的单个标准封装件,从而形成一个系统或子系统。

这个解释与Chiplet非常相似,两者都是采用封装技术进行芯片组合,区别究竟在哪里?

通富微电总裁石磊认为,在广义的封装基础上可将Chiplet视为SiP的一种,因为SiP的范围非常广泛,多die,die和被动器件合封都是SiP。“现在提到的Chiplet是强调把超大尺寸die设计成多个中/大尺寸die,再进行晶圆制造和封装加工,是从细分角度考虑。而通常提及的SiP,最典型的是手机里的各模块,其主要特点是把大量小尺寸(及不同功能)的小die和大量的被动器件封装在一起,主要是强调模块高集成化。”石磊告诉集微网。

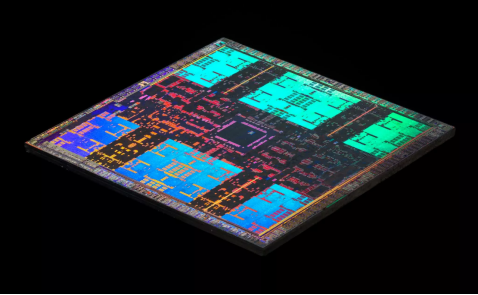

一个典型的Chiplet就是AMD的Zen2架构处理器,其CPU核心与I/O核心分离制造,CPU使用了台积电7nm工艺,I/O则是格芯的14/12nm工艺,两者最后封装成单一芯片。

从中也看出了两者之间的差异。云天半导体董事长于大全认为Chiplet重在拆分组合,“芯片的功能单元被分出来,然后再重新整合成一个完整功能的芯片,相当于一个物体拆成很多积木,然后又搭成一个新东西出来。”

“可以认为SiP涵盖了Chiplet的很大部分,但有一部分没有被考虑。”于大全强调。

在封装层面,Chiplet还是与SiP有很多相似之处,都采用了大量先进封装技术。与之相应,封装层面的挑战也随之而来。

在石磊看来,Chiplet虽然避免了超大尺寸die,同时也意味着超大尺寸封装,又高度融合晶圆后道工艺,更在封装Micro-bump、多layer 扇出FO、超多芯片FC等方面带来了极限技术挑战,如封装加工精度和难度进一步加大,工艺窗口进一步变窄,通用设备比例降低,设备升级需求大等。

于大全也认为技术挑战将加大,“将不同的芯片放在硅interposer(中介层)上,是目前高性能Chiplet的主要选择,但怎么把芯片的高速接口连接在一起,就需要特定的协议,需要微凸点的制造技术,需要芯片堆叠技术,需要TSV制造技术,这些实现起来很有挑战性。”

于大全表示:“还有一类广义的Chiplet,比如把CPU加上memory放在一起,可以用TSV(硅过孔)也可以用Fan out(扇出型封装)来做,但是对布线的精度要求就很高了,如TSV的布线精度在1μm以下,Fan out的布线技术在2μm左右,这就是Chiplet需要解决的关键封装问题。”

最后一个挑战在于高可靠性,“因为Chiplet中的芯片变多了,连接的点变多了,界面也就变多了,可靠性问题是非常严峻的。”于大全特别指出。

除此之外,散热和功率分配也是需要考虑的巨大问题,Chiplet要继续前进,先进封装技术还要解决很多挑战。

封装厂:机遇与挑战并存

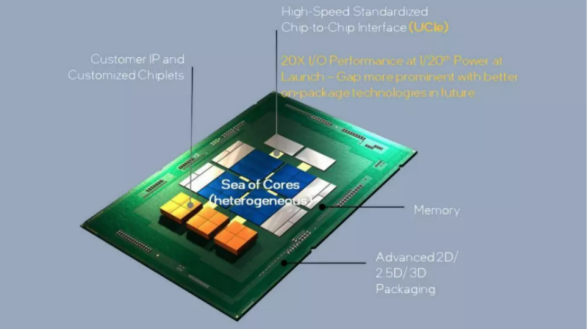

UCIe联盟为Chiplet指定了多种先进封装技术,包括英特尔EMIB、台积电CoWoS、日月光FoCoS-B等。这也折射出一个现实,围绕先进封装的竞争越来越激烈。

调研机构Yole发布的《2021年先进封装行业现状报告》中指出,虽然OSAT主导着先进封装市场,在初制晶圆方面OSAT约占整个市场的70%。然而,在高端封装领域,包括2.5D/3D堆叠、高密度扇出,大型代工厂(如台积电)和IDM(如英特尔和三星)在高端市场发展迅速,占据了市场主导地位。

台积电近年来成为封装技术创新的引领者,从CoWoS到InFO,再到SoIC,与苹果、AMD联手打造多个明星产品,英特尔也在多款产品中运用了自研的先进封装技术。一时间,前道封装技术风光无限。所以,很多人自然会质疑OSAT(委外封测代工厂)在Chiplet封装中逐渐会边缘化。

封装厂商并不认可这个观点。石磊认为:“Chiplet融合了晶圆厂部分中后道技术,所以台积电为代表的晶圆厂推出了封装解决方案,但Chiplet多数环节还是基于传统和先进封装,封装厂的经验积累和制造加工也特别重要。同时,晶圆加工注重通用和归一,而封装注重客户个性化需求,能灵活发展各类封装技术专长,快速提供满足市场需求的Chiplet产品,封装厂发展Chiplet是大有可为之处的。”

长电科技对集微网表示,“我们看到这两三年,前道制造和后道制造,包括设计,都在积极地参与到异构集成,2.5D、3D封装这样的一个联合阵线上来。这反映了一个产业协同向前发展的必然趋势。前道制造在后前走,后道制造也在向前走的时候,难免中间会出现共通的领域。但大方向毫无疑问是前道制造做前道制造擅长的事情,后道制造做后道制造擅长的事情,最后把Chiplet形成最后的芯片成品,这就肯定还是要由做最后成品的企业来做这件事情。”

“Chiplet变成一个Chip之后,还要做封装,不管是Fan Out也好,BGA也好,所以像台积电这样的企业还会找封装厂合作,因为自己根本封装不完这么多芯片,这就给了封装厂大量的机会。”于大全也持相似观点。

据一位业内人士判断,如果等近年来新建晶圆厂都释放产能后,会有大量加工后的晶圆流向后道封装厂,因此后道先进封装市场仍有较大提升空间。

同时,为了和晶圆厂相抗衡,封装厂也在开发自己的先进封装技术,如扇出型封装技术。虽然命名各异,但是各大封装厂都已经拥有了自己的扇出型封装技术(请参看《集微咨询:扇出型封装正在变得无处不在》一文)。

石磊认为,板级和晶圆级扇出型封装都是封装厂参与Chiplet的利器,全球最顶尖的几家OSAT Chiplet技术开发工作都做得不错。而且,当前芯片设计公司和封装厂都在紧密配合大力发展Chiplet封装。

长电科技也表示,公司在将近20年前已经开展了晶圆的封装技术,海外的工厂也是当时最早和台积电一起对扇出型晶圆级封装技术投入了巨资,进行了大量的专利和技术开发的工作。所以,确实这是产业未来发展的一个潮流。

不过,于大全也指出封装厂做先进封装的优势不太明显,因为越来越多的Chiplet是在有源芯片上做通孔或互联,交由封装厂来做会导致风险过高。

总体而言,OSAT面临前道企业在先进封装技术领域的竞争,必须寻求对应低成本高性能封装技术,展开差异化竞争,才能在激烈的竞争中不断发展。

大陆封装业:在Chiplet上实现共赢

大陆地区的封装行业已经在全球占据了非常重要的地位,在Chiplet的封装方面表现如何呢?

“大陆Chiplet封装技术相比业界顶级厂商还有差距,但不是很大。扇出型FOMCM和多芯片FCMCM已达到了较高水准,基于硅interposer和硅bridge(桥)的2.5D/3D技术也在发展中。”石磊表示。

需要注意的是,国际顶尖企业是在先进制程的基础上进行Chiplet的封装,大陆地区的晶圆制造尚在追赶先进工艺的路上。

“这也不代表我们没机会,如果能在28nm平台上实现Chiplet也是件好事,就不需要14nm、7nm工艺了,但这也需要有相关企业来推动这件事情的发生。”于大全认为。

不过,对于UCIe联盟的成立,厂商们还是给出正面的评价。长电科技表示,Chiplet还是需要形成一个事实上的标准化流程,以避免在市场规模还比较小的过程当中造成资源和技术的浪费,UCIe是一个非常好的方向。

石磊表示,“UCIe技术联盟的成立时间还比较短,我们看到联盟中也有OSAT,乐观认为其能促进Chiplet生态圈的良性发展,能对OSAT封装技术发展起到积极作用。”

集微网从采访中也获知,UCIe联盟的成立是全球半导体行业的大事,大陆的产业链也正积极参与其中。长电科技表示,UCIe联盟有逐步公开参加成员的流程,大家后边会看到包括长电科技在内,其他国内厂家都在积极地参与标准制定。并且,包括UCIe在内的几个不同标准化制定工作也都有国内厂商所参与。

长电科技还希望业界对这个标准要保持耐心,“小芯片本身也还是刚刚起步,而标准化的工作是一个非常漫长的过程,我们要用发展的眼光来看待Chiplet相关的标准化工作。这种标准化应该由具有适当技术能力的 OSAT或封装流程执行。”

石磊也指出,鉴于UCIe/Chiplets技术的复杂和难度,业界各环节的顶尖企业成立联盟去讨论解决一些问题,因此各环节一定不要独立盲目的去发展UCIe,应持有一个开放、包容和共赢的态度!”

最后,于大全认为整个Chiplet产业链都需要加强,“Chiplet实际上整合了很多技术,包括设计、制造、封装等,所以整个产业链条都要往前发展,这样才能最终实现自己的Chiplet。”(校对/Andrew)