国际学习表征会议(International Conference on Learning Representations,ICLR)是机器学习与人工智能领域的重要国际学术会议之一,主要关注深度学习、表示学习及其在各类交叉学科中的前沿进展。ICLR 2026 于 2026 年 4 月 23 日至 27 日在巴西里约热内卢举行。

近日,计算所李华伟研究员-穆嘉楠特别研究助理课题组联合香港中文大学余备教授课题组、北京大学王润声教授-林亦波研究员课题组完成的论文在 ICLR 2026 发表。该工作提出并构建了 CircuitNet 3.0,一个面向 AI 驱动芯片设计的大规模、多阶段、多模态开源数据集,为机器学习方法在芯片设计自动化领域的研究与评测提供了更加完整的数据基础。论文共同第一作者为计算所 2025 届毕业生王铭珺(目前在香港中文大学攻读博士学位)和香港中文大学博士生文一涵。计算所特别研究助理穆嘉楠为论文共同通讯作者。

集成电路设计需要将高层功能描述逐步转化为可制造的物理版图,流程复杂、周期漫长,对工程经验和专业 EDA 工具依赖程度较高。近年来,AI方法在芯片设计自动化领域(AI for EDA)展现出重要潜力。然而,该方向的进一步发展受到公开数据集不足的制约:现有数据多集中于单一设计阶段或单一数据模态,难以支撑跨阶段、跨抽象层的模型研究与系统评估。

围绕这一问题,北京大学团队已提出 CircuitNet 1.0 和 CircuitNet 2.0 数据集,为机器学习在芯片设计自动化领域的应用提供了重要基础。其中,CircuitNet 2.0 在物理设计阶段引入了大规模的先进工艺数字电路版图数据,支持多项后端任务。然而,现有版本在 RTL 设计多样性、跨阶段数据对齐以及多模态联合建模等方面仍存在不足,限制了其在早期设计分析和跨抽象层学习任务中的应用。

针对上述挑战,论文提出并构建了 CircuitNet 3.0。该数据集以 8,659 个通过综合与仿真验证的高质量开源 RTL 设计为基础,借助工业级 EDA 流程生成了超过 15,000 个完整设计实例,覆盖从 RTL、门级网表到物理布局的关键设计阶段。每个设计样本同时包含 RTL 代码与文本描述、结构化图表示以及版图图像表示,并配套提供经过 EDA 流程验证的时序与功耗指标,实现了从 RTL 到 Layout 的全流程数据对齐与可追溯。

在数据构建方法上,论文提出了一种面向 EDA 任务的数据增强与筛选框架。在 RTL 阶段,采用基于 Verilog 抽象语法树的结构化重写方法,在保证可综合性和功能正确性的前提下,高效生成多样化设计样本;在综合网表与物理设计阶段,进一步引入以时序和功耗为目标的多阶段优化与筛选机制,重点保留关键路径紧张、功耗敏感等具有较高工程价值的设计样本,从而提升数据集在实际工业设计场景中的代表性。

基于 CircuitNet 3.0,论文系统评估了多种单模态与多模态机器学习模型在时序预测和功耗预测任务上的表现。实验结果表明,相比已有数据集,CircuitNet 3.0 能够为模型提供更完整的跨阶段、多模态设计信息,从而提升时序与功耗预测精度。其中,代表性时序指标的预测误差最高降低约 36.0%,总功耗预测误差降低约 12.9%。这一结果验证了高质量跨阶段数据对于 AI for EDA 任务的重要价值,也表明任务驱动的数据构建策略能够有效提升模型在芯片设计场景中的应用效果。

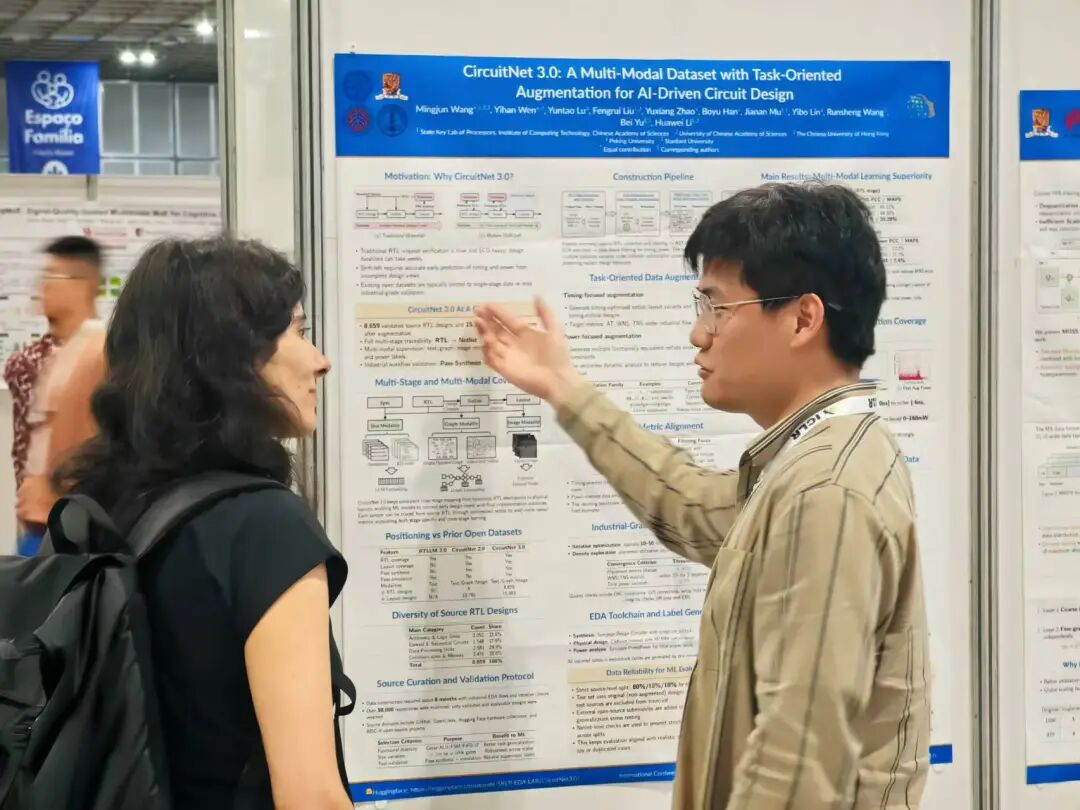

图:穆嘉楠特别研究助理在 ICLR 2026 会议现场介绍 CircuitNet 3.0,并与国际同行交流讨论

CircuitNet 3.0 数据集地址:

https://github.com/sklp-eda-lab/iclr-circuitnet_3.0/

处理器芯片全国重点实验室依托中国科学院计算技术研究所,是中国科学院批准正式启动建设的首批重点实验室之一,并被科技部遴选为首批 20个标杆全国重点实验室,2022年5月开始建设。实验室学术委员会主任为孙凝晖院士,实验室主任为陈云霁研究员。实验室近年来获得了处理器芯片领域首个国家自然科学奖等6项国家级科技奖励;在处理器芯片领域国际顶级会议发表论文的数量长期列居中国第一;在国际上成功开创了深度学习处理器等热门研究方向;直接或间接孵化了总市值数千亿元的国产处理器产业头部企业。