PCIe最近几年发展非常快,年初6.0协议标准定稿时,4.0设备也只是刚刚开始导入。忆芯科技上半年流片的新一代高性能企业级SSD主控芯片STAR2000,就是基于PCIe 4.0标准,其性能较之前的产品提升一倍。之后立即就启动了PCIe5.0 STAR1500主控的研发,前端带宽又有一倍的提升。

今天我们就来聊聊PCIe 5.0协议一些主要更新,这些更新集中于物理层,包括有序集,均衡,预编码和备用协议协商等。

一 ► 有序集

有序集更改是5.0版本的一项重要修改。EIEOS有序集(Electrical Idle Exit Ordered Set)的pattern相对4.0的16个连续的0/1序列变为32个连续的0/1序列(如下图所示)。同时两个EIEOS必须是背对背连续出现的。

(图片来自PCI-SIG)

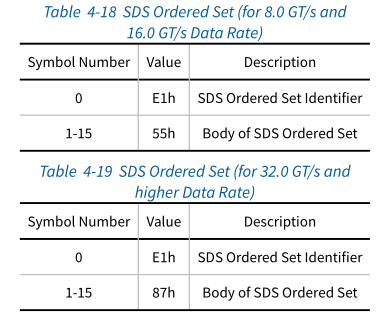

SDS(Start of Data Stream Ordered Set)符号1-15的内容从0x55修改为0x87。

(图片来自PCI-SIG)

SKP(Skip Ordered Set)符号0-11的内容从0xAA修改为0x99。

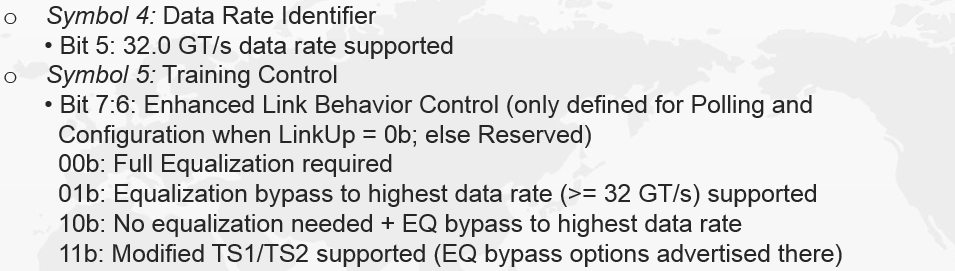

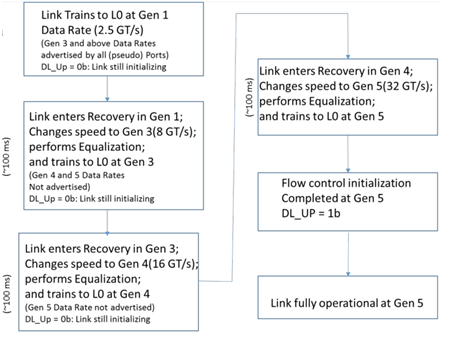

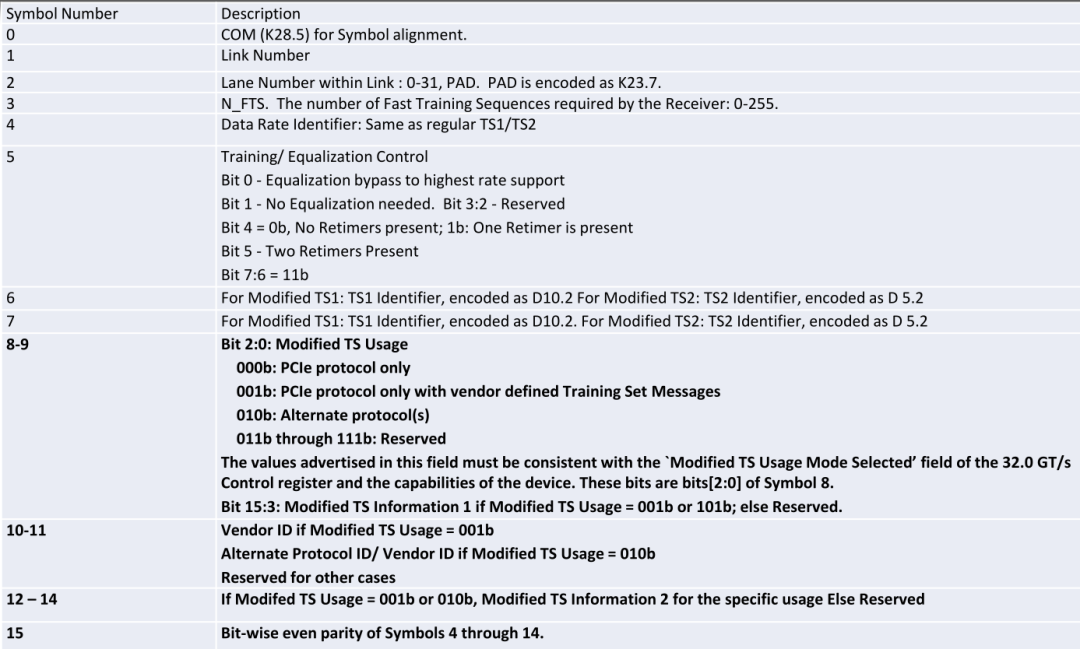

TS1/TS2 Ordered Set不同的符号位还有下面的一些修改。

(图片来自PCI-SIG)

符号5的变化用于协商EQ旁路/修改TS1/TS2协商(用于备用协议协商等事情),而符号6和7的变化是用于预编码。

(图片来自PCI-SIG)

二 ►均衡(EQ)

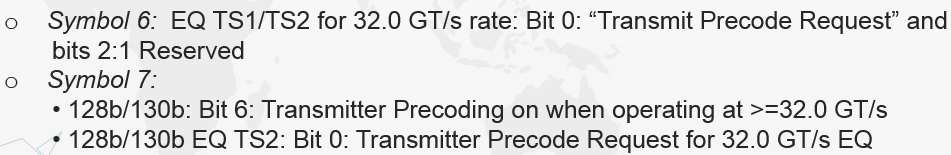

均衡的流程也增加了新的选项。Full-EQ过程如下图所示,从Gen1到Gen3的EQ,然后是Gen3到Gen4的EQ,最后是Gen4到Gen5的EQ,逐次进行,这个过程的时间相较于Gen3/Gen4会更长,同时对于只工作在Gen5的链路而言,中间Gen3/Gen4的EQ过程也会显得有些浪费时间。

(图片来自PCI-SIG)

为了解决延迟问题,5.0规范提供了旁路选项,如下图所示,可以跳过Gen3和Gen4的EQ过程,直接进行从Gen1到Gen5的一次EQ。只有链路两端都支持时,才可以采用这种旁路模式,否则还是会按照Full-EQ模式进行均衡和训练。对于两端都支持Gen5或以上速率的设备,如果把目标设置为Gen3或Gen4的速率,不建议采用旁路模式。

(图片来自PCI-SIG)

还可以通过设置No EQ位来跳过所有EQ的过程,直接切到Gen5速率,能够大大节省时间。如果本地存有之前预设好的均衡参数值,或者对链路的质量有足够的信心,可以采用这种模式。

三 ►预编码(Precoding)

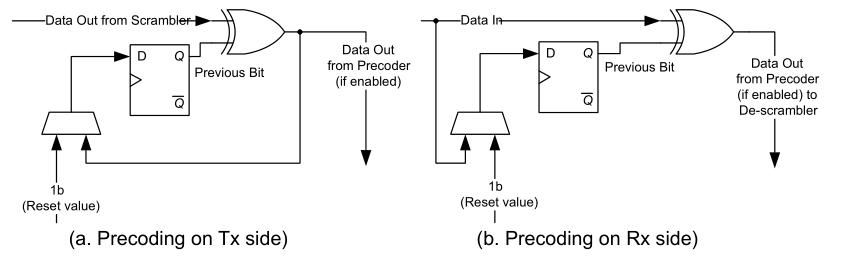

PCIe接收端采用DFE(反馈判决均衡器)进行判决,在Gen5速率下比Gen4更容易发生Burst Error(突发错误)。为了减少连续突发错误的发生,Gen5速率下可以启用Precoding。Precoding仅适用于Gen5及以上速率。PCIe Rx侧通过EQ TS2请求Tx开启Precoding。

Precoding存在于Tx Scramble之后、Rx De-scramble之前。开启Precoding不会影响信号质量及完整性。PCIe Precoding示意图如下:

(图片来自PCI-SIG)

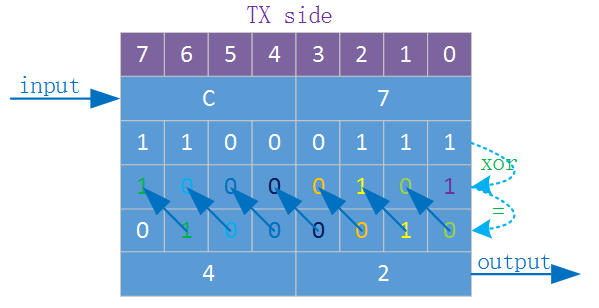

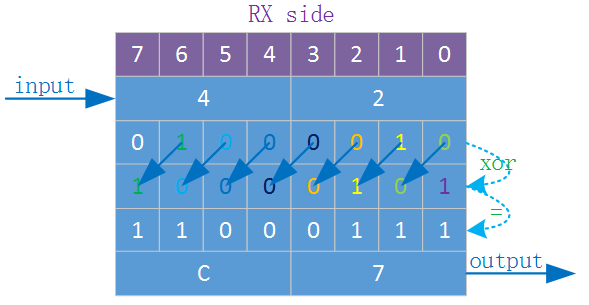

从加扰器(Scrambler)出来的bit,与前一个输出bit进行异或再发送,对于没有前一个bit的第一个bit,则与1进行异或。发送侧生成过程如下图来所示:

接收到的bit与前一个接收到的bit进行异或输出,对于没有前一个bit的第一个bit,则与1进行异或。接收侧生成过程如下图来所示:

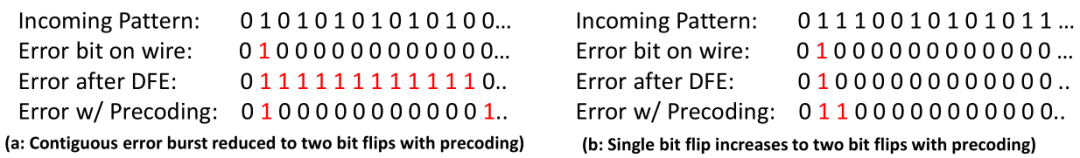

Precoding可以把连续多bit的Burst Error转化成2 bit的start Error及 end Error,从而达到消除Burst Error的目的。对于单bit的错误,开启Precoding后会变成2 bit错误,从而使系统误码率BER会提升到之前的两倍。

(图片来自PCI-SIG)

四 ►备用协议协商

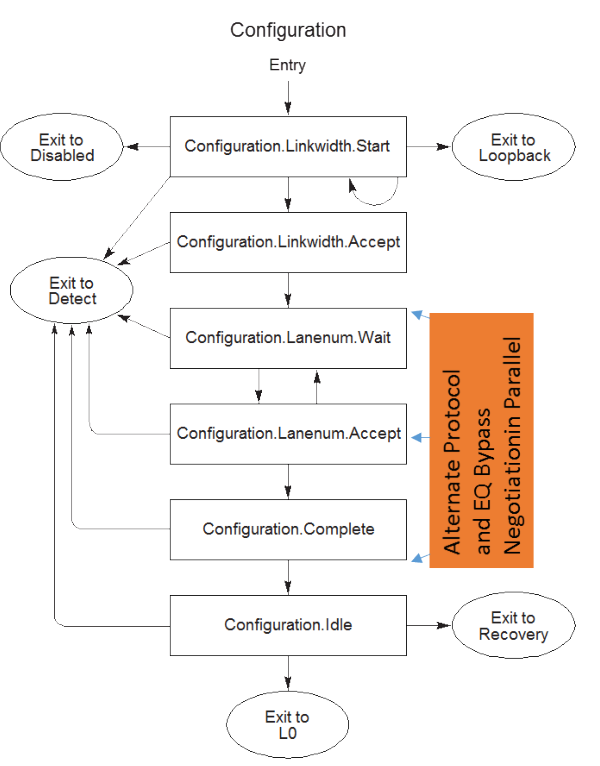

备用协议协商(Alternate Protocol Negotiation),Alternate Protocol是指运行在PCIe上的非标准协议,目前有CXL协议。采用Modified TS1/2,跟Cfg.Lanenum.Wait、Cfg.Lanenum.Accept、Cfg.Comple并行,同时旁路EQ。

Modified TS1/2如下图所示:

(图片来自PCI-SIG)

备用协议协商状态机如下:

(图片来自PCI-SIG)

当系统和设备之间的协商成功,链路就可以立即以支持的最高速度进入L0状态,并开始使用协商的备用协议传输数据。

登录

登录