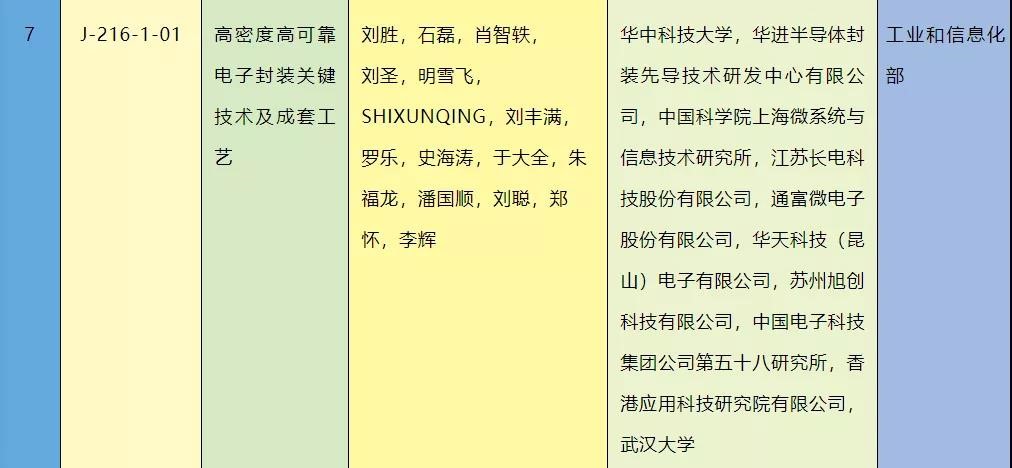

集微网消息,11月3日,2020年度国家科学技术奖励大会在北京举行。其中,由华中科技大学、华进半导体封装先导技术研发中心有限公司、中国科学院上海微系统与信息技术研究所、江苏长电科技股份有限公司、通富微电子股份有限公司、华天科技(昆山)电子有限公司等高校、企业及科研单位合作完成的“高密度高可靠电子封装关键技术及成套工艺”项目获国家科学技术进步奖一等奖。

图片来源:锐科技

华中科技大学消息显示,项目团队针对高密度芯片封装翘曲和异质界面开裂导致的低成品率,提出芯片-封装结构及工艺多场多尺度协同设计方法和系列验证方法,应用于5G通讯等领域自主可控芯片的研制,攻克了晶圆级扇出封装新工艺,突破了7nm CPU芯片封装核心技术。项目解决了电子封装行业知识产权“空心化”和“卡脖子”难题,占领了行业技术制高点,实现了高密度高可靠电子封装从无到有、由传统封装向先进封装的转变,具备国际竞争能力。此外,项目完成单位与国内企业合作研制了系列封装及检测设备,建立了多条封装柔性产线;300多类产品覆盖通讯、汽车、国防等12个行业。

作为第二完成单位,华进半导体消息显示,公司在该项目中承担核心技术研发角色,针对光子器件、电子器件封装的协同设计方法和集成技术开展了深入的研究。通过对光、电、热、应力等多物理场参量建模以及测试技术的研究,掌握和具备了设计仿真、工艺制备、测试验证等关键技术,并搭建了从研发到量产的中试平台,特别对非气密光电异质集成封装、射频微波组件、多芯片混合三维集成等高性能产品应用方面有贡献。

作为主要完成单位,通富微电子消息显示,此次获奖项目内容之一是针对高密度芯片封装工艺中焊点易桥连和界面易损伤难题,提出倒装铜柱凸点高密度键合技术,发明原位微米级栅线投影翘曲测试方法,研制基材与布线密度匹配、磁性载具与回流曲线优化的低应力倒装焊接工艺,产品成品率达 99.8%。项目来源于通富微电子承担的2017年国家02专项——CPU封装及测试技术开发。(校对/若冰)

登录

登录