先进封装不是摩尔定律失效的救世主,也并非与先进工艺互斥的新技术路径,其本质意义是挖掘芯片制造过程中的潜能,将传统封装中被延缓的数据传输速度和被损耗的大量功耗,通过技术和结构的创新极大程度的找回。

与前道先进工艺不断迭代类似,“先进封装”其实也是一个模糊和长期变化的概念,每个时代的“先进封装”都意味着一次技术体系革新。例如,过去DIP、SOP、TSOP、QFP、LQFP等技术被看作传统封装时,BGA、CSP、FC、MCM(MCP)等技术就会被称为“先进封装”。

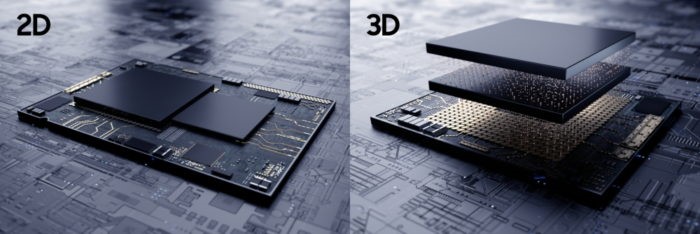

而时下被广泛提及的“先进封装”,实际是一次平面封装向2.5D/3D堆叠异构集成封装技术的升级跃迁。

缘起台积

如今的“先进封装”概念并非由封装厂提出,其最早诞生于2009年的台积电。当时台积电团队发现,在传统封装基板上的引线线宽超过50μm,随着逻辑芯片和存储芯片之间的数据传输量越来越大,高线宽会导致整颗芯片约40%的传输速度和60%的功耗被白白浪费。

而假如用硅中介层来替代传统基板,将逻辑芯片和存储芯片等堆叠封装,引线线宽能够缩小至0.4μm以内,被损耗的大部分传输速度和功耗都能被重新找回。

一位业内人士告诉集微网,该团队负责人与当时台积电的董事长张忠谋针对先进封装项目仅沟通了1小时左右,后者便给予了400人团队布建和1亿美元资本投入的承诺。基于使用硅中介层的3D堆叠,台积电于2012年推出了CoWoS封装技术,但由于成本较高而难以推广。随后又推出了主要针对手机芯片的InFO封装技术,采用聚酰胺薄膜代替CoWoS中的硅中介层,从而降低了单位成本和封装高度。

图源:DIGITIMES

CoWoS和InFO先进封装解决方案,不仅为台积电的先进工艺之虎插上双翼,还帮助其与越来越多的客户深度绑定。其中,台积电先进封装技术最著名的一“战”便是吃光三星的苹果A系列处理器代工订单。

早在2015年时,苹果的A9处理器还分别交由三星的14nm和台积电的16nm代工。而一年之后,台积电竟在沿用16nm工艺的前提下包揽了苹果A10处理器的所有代工订单。从分庭抗礼到独霸天下,只因台积电在A10芯片上全面启用了自研的InFO FOWLP封装技术,在逻辑工艺并没有升级迭代的情况下,A10芯片仍然实现了40%的性能提升,并延长iPhone的待机时间。

2016年至今,台积电先进工艺不断下探的同时,先进封装技术也在不断升级,两者的相辅相成让苹果、AMD、英伟达等国际巨头都与台积电形成了长期的深度绑定。

一步步坐实晶圆制造龙头身份,台积电的一举一动显然会牵扯着各方神经,唯二能与之抗衡的Intel和三星也在晶圆制造后道的先进封装领域展开大规模投资布局。

谁是主力?

台积电下场发力封装业务,三星跟进的X-Cube技术步步为营,Intel基于先进封装技术进行架构变革,晶圆厂整齐的步伐彰显出了芯片制造商对于性能和功耗的极致追求,同时也让传统封装厂陷入尴尬境地。

图源:三星X-Cube技术

究竟是封测厂拿不动“刀”了,还是晶圆厂要求太高了呢?其背后还与先进封装本身的技术特征有关。

从技术角度来看,传统封装中的各类芯片都是水平互联,而先进封装中芯片堆叠后的互联,以及芯片向下连接基板时,都需要一种垂直互联的方式来提高系统的整合度和效能。目前, 业界主要依靠TSV(硅通孔)技术来实现。

TSV技术通过在硅中介层上以蚀刻或激光的方式钻孔,再以导电材料如铜、多晶硅、钨等物质填满,堆叠的芯片便能通过被填充的硅通道实现垂直互联。与以往的IC封装键合和使用凸点的叠加技术相比,TSV能够使芯片在三维方向堆叠的密度最大,外形尺寸最小,并且大大改善芯片速度和低功耗的性能。在现有的先进封装方案中,不论是台积电的CoWoS,还是Intel的Foveros 3D技术、三星的X-Cube技术,都需要用到TSV技术。

正是因为TSV技术对于时下的先进封装各类体系不可或缺,加之晶圆厂在硅中介层制造上具有先天优势,因此主流晶圆厂的封装事业部纷至沓来。

“由于技术和结构的特殊性,先进封装既需要晶圆制造工序,又需要常规封装工序,这也意味着无论是晶圆厂还是封装厂,要想进军先进封装事业就需要补充学习对方的长处。”一位先进封装领域资深人士告诉集微网,“而由于晶圆制造业所涉及的学科数量、工艺工程的复杂程度都远高于封装业,因此晶圆制造厂学习封装的技术难度,远低于封装厂学习晶圆制造的技术难度。”

既然是跨领域的技术,晶圆厂与封装厂是否能够在先进封装领域继续建立长期的分工合作关系呢?

一家台系晶圆厂内部人士指出,晶圆厂与封装厂在先进封装领域是无法建立长期合作关系的,原因包括以下两点:

首先是良率不统一、责任难以划分的问题。晶圆厂与封装厂很难做到良率统一,倘若晶圆厂完成生产后再运输到封装厂进行先进封装,则芯片的最终良率需要由双方共同负责,而由于两者本身良率存在差异,故晶圆厂和封装厂无法在良率不对等的情况下长期合作。

其次,先进封装对于芯片效能的提升显而易见,晶圆厂正凭此跑马圈地,并期待与更多的大客户形成深度绑定。也就是说,当掌握了领先业界的先进封装技术时,晶圆厂能迎来更多、更稳定的代工订单。因此,主流晶圆厂很难再将如此重要的先进封装任务放手交由封测厂。

晶圆厂的“入侵”势必会在一定程度上挤压封装厂未来的业务成长空间,因此大陆外一线封装厂也开始在先进封装领域追逐角力。不过,封装厂提及的“先进封装”更为广义化,其将倒装(FC)、芯片尺寸封装(CSP)、系统级封装(SiP)以及基于玻璃等材料的晶圆级封装(WLP)技术亦称之为先进封装。

封装厂推动的先进封装技术虽有所进步,但仍与晶圆厂所主导的先进封装有所差距。以封装厂的晶圆级封装为例,在硅中介层的重布线层,不仅单位面积内Die的数量更高,其线宽的极限(1.8/1.8μm及以下)也远低于有机材质或玻璃(4/4μm及以上)。这也意味着,晶圆厂基于硅中介层的先进封装技术将拥有更高的D2D互连密度。

前述台系晶圆厂内部人士告诉集微网:“超低线宽才是先进封装的终极奥义,而目前只有晶圆厂能在硅中介层上将线宽降至1.8/1.8μm以下。至于为何一定是1.8/1.8μm,这主要因为越来越多的芯片厂选择将CPU / GPU / TPU与一个或多个高带宽内存(HBM)组合在一起进行先进封装,而业界目前HBM对线宽的最低要求便是1.8/1.8μm。”

大舞台和更大的舞台

先进封装的技术创新一半体现在2.5D/3D堆叠,另一半还体现在异构集成,两者缺一不可。

倘若只谈堆叠,早在2006年,三星就通过TSV技术就将8个2Gb NAND Flash堆叠封装成同一颗芯片。而台积电CoWoS技术的早期客户赛灵思也仅是用四块同样的FPGA芯片堆叠,台积电先进封装团队对此喜忧参半,喜的是有客户愿意采用这项新技术,忧的是这种同质堆叠无法让CoWoS展现全部实力,直到迎来第一个使用CoWoS技术进行异构集成的客户华为海思,台积电的这项先进封装工艺才终于开始名声大噪。

因此,基于2.5D/3D堆叠的异构集成才是完整的先进封装结构。在这两项特征的加持下,高端芯片是先进封装的一个大舞台。

5G、自动驾驶、人工智能和高性能计算等新应用的蓬勃发展催生了海量数据,这些数据需要不仅需要在芯片内部运算,还需要进行存储。DDR已经很难提供芯片厂需要的高带宽,IO瓶颈越来越严重,于是芯片厂选择将CPU / GPU / TPU与一个或多个高带宽内存(HBM)组合封装,以使带宽不再受制于芯片引脚的互联数量,并带来更低的延迟和功耗。

目前,AMD、英伟达、英特尔等芯片厂商的高端芯片都采用了先进封装技术,且据业内人士透露,目前几乎所有在台积电流片的高端 AI芯片都会选择CoWoS技术。

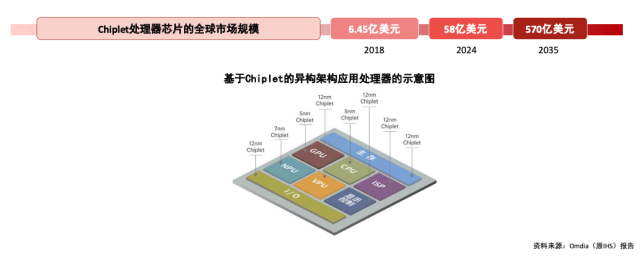

放眼未来,Chiplet这一未来趋势更将为先进封装创造更大的舞台。芯原股份董事长戴伟民曾多次在公开场合表示,并非每种芯片都需要尖端工艺,因为不是每一家公司都能负担起7nm、5nm工艺的成本,于是Chiplet这种将不同工艺节点的die混封的新形态是未来芯片的重要趋势之一。

戴伟民强调,封装和接口对于Chiplet至关重要,台积电的CoWoS技术和英特尔的Foveros 3D立体封装技术都为Chiplet的发展奠定了基础。

据Omdia报告,Chiplet处理器芯片的全球市场规模正在井喷式增长,预计到2024年会达到58亿美元,2035年则超过570亿美元。

站上起跑线

在封测厂所定义的先进封装中,长电科技等大陆厂商正与日月光、安靠等大厂齐头并进。但在本文所探讨的晶圆厂主导下的先进封装层面,目前全球仅有台积电、英特尔和三星能提供完整的先进封装平台,中国大陆晶圆厂仍站在起跑线外。

值得一提的是,中国大陆晶圆代工龙头厂商似乎已经释放出积极信号。中芯国际资深副总裁张昕日前在IC WORLD大会上提及其6大平台时指出:“公司先进封装平台将在2.5D领域提供全覆盖Interposer方案,3D IC提供HBM/近存计算解决方案。”

晶圆厂布局先进封装已是大势所趋,对于先进工艺遭遇严重遏制的中芯国际而言,发力先进封装不仅是顺应产业潮流,更是拉长战线、提高自身业务水平的战略需要。

先进封装不仅将为中芯国际等大陆晶圆厂创造新的机遇,也将为上游的材料、设备以及EDA厂商带来挑战和发展机遇。以设备为例,中芯国际等晶圆厂布局先进封装平台需要用到大量的封测设备,例如贴片机、引线焊接设备等,而出于供应链安全考虑,国产设备势必将是未来的主要供应商,上下游协同发展才能取得成功。

值得一提的是,设备厂商华封科技在先进封装领域已经有所斩获,其贴片机设备已经通过了台积电、长电科技等厂商的技术验证,并获得了日月光、矽品、通富微电等头部厂商的批量采购。

另外,在EDA方面,先进封装作为一个新的领域,之前并没有成熟的设计分析解决方案,使用传统的、脱节的点工具和流程对设计收敛会带来巨大的挑战,而对信号、电源完整性分析的需求也随着垂直堆叠的芯片而爆发式增长。因此,先进封装需要用到前所未有的EDA平台,这对于国产EDA厂商而言是一个突围的机会。

日前,本土EDA厂商芯和半导体举行的年度用户大会上,该公司CEO凌峰曾介绍称,支持先进工艺、先进封装一直以来是芯和半导体的产品方向。该公司推出的IRIS、iModeler,及Metis系列产品均能够完美的支持先进工艺和封装。

不难看出,本土供应商都已经率先“闻”到了先进封装这一重要技术趋势,且先后开启了相关业务布局。上游供应商率先站上起跑线,晶圆厂紧随其后,这种健康、符合产业逻辑的发展方式,为中国本土先进封装技术奠定了基础。

长久以来,晶圆制造一直是我国半导体产业的落后环节,封装技术却是大陆半导体行业中与全球顶尖技术之间差距最小的环节。在国际主流晶圆厂入局先进封装后,封装技术差距也有被进一步拉大的趋势。在此情形下,本土晶圆厂在追赶先进工艺的同时,必须与国际主流厂商保持步调一致,否则未来中国半导体产业将面临制造、封装技术双重落后的危机。(校对/叨叨)

登录

登录