集微网消息 集微直播间自开播以来获得了大量来自行业的关注与好评。其中“集微公开课”栏目联合行业头部企业,通过线上直播的方式分享精彩主题内容,同时设立直播间文字提问互动环节。集微网希望将“集微公开课”栏目打造成中国ICT产业最专业、优质的线上培训课程,深化产教融合,助力中国ICT产业发展。

第33期“集微公开课”于8月11日(周二)上午10:00直播,邀请到成都锐成芯微科技股份有限公司首席技术长谢建棋,带来以《有线高速信号传输概要》为主题的精彩演讲。

经过多年的发展,成都锐成芯微科技股份有限公司IP平台逐渐完善,目前包括超低功耗模拟IP、超低功耗RF、高可靠性eNVM和高速高性能接口IP四个核心模块。

在此次集微公开课中,成都锐成芯微首席技术长谢建棋进一步解读了锐成芯微在高速高性能接口IP方面的技术和布局。

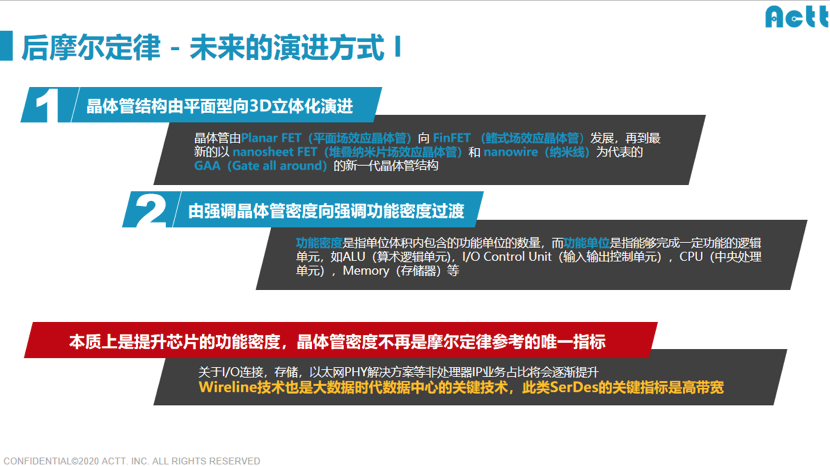

后摩尔定律时代的探索

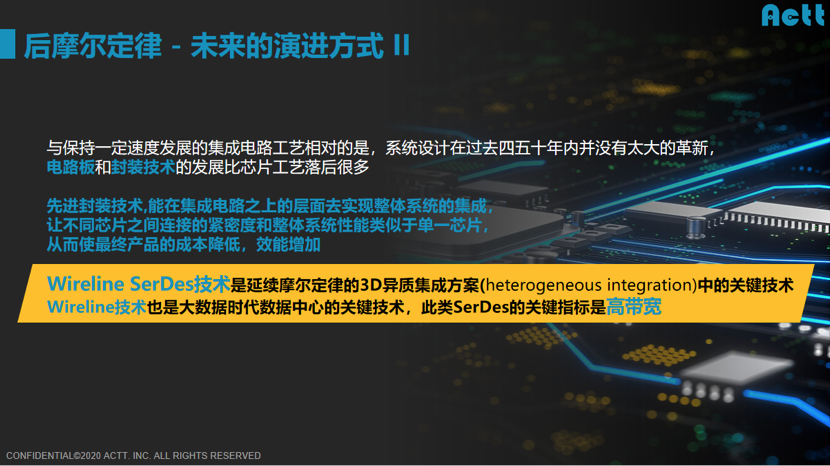

从摩尔定律在1965/1975被戈登·摩尔两次提出,到现在四五十年时间里,摩尔定律一直引领产业发展。如今摩尔定律已经很接近其物理极限,虽然半导体仍会继续创新,但不会像以往这么快。其创新的本质上是提升芯片的功能密度,晶体管密度不再是摩尔定律参考的唯一指标。

因此,半导体行业提出了异质集成的方法,将不同功能的IC集成到单一芯片中,以形成系统或子系统,3D-IC异质集成技术中。

在此情况下,I/O连接、存储、以太网PHY解决方案等非处理器IP业务占比将会逐渐提升,加之5G、物联网技术的快速发展,全球数据流动的规模和速率都在飞速增长,SerDes技术的重要性也越发凸显。Wireline SerDes技术成为延续摩尔定律的3D异质集成方案中的关键技术。

谢建棋表示,Wireline技术也是大数据时代数据中心的关键技术,此类SerDes的关键指标是高带宽。

SerDes市场趋势与设计关键

SerDes是Serializer串行器/Deserializer解串器的简称,可以让数据以高速串行信号的形式进行长距离传输,解决了以往多设备之间并行传输过程中导致的信号差错、时间混乱的问题,从而提升数据网络内的传输速度。

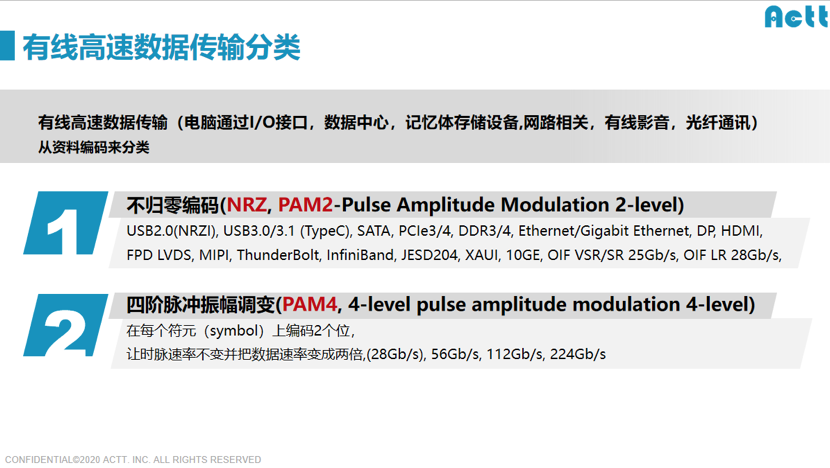

SerDes的应用广泛,涉及电脑I/O接口、数据中心、存储设备、网络相关,有线影音、光纤通讯等领域。按资料编码来分类,又分为不归零编码(NRZ、PAM2)和四阶脉冲振幅调变(PAM4)两类。

过去几年,SerDes在速度方面虽取得了大幅的进展,从10Gbps、28Gbps到56Gbps,但提高SerDes IP的数据传输速率和节省带宽仍迫在眉睫。

谢建棋表示,SerDes市场规模在2018年为4.96亿美元,到2026年,全球SerDes市场预计将达到8.458亿美元。

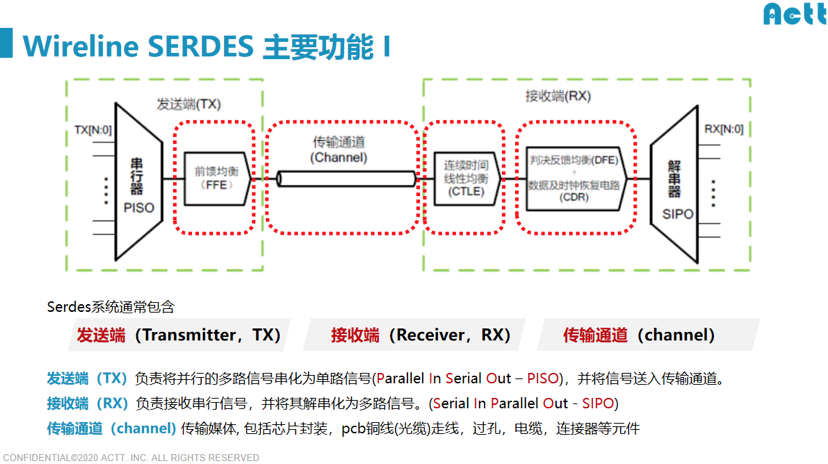

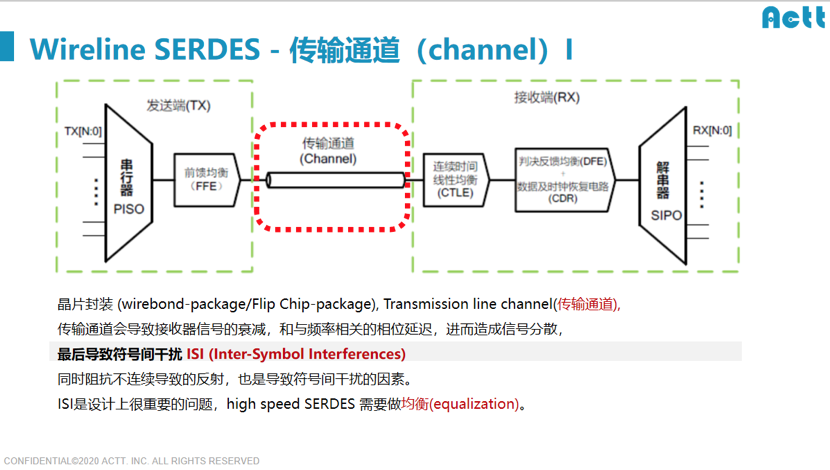

Serdes系统通常包含发送端(TX)、接收端(RX)、传输通道(channel)。

信号在传输通道传输过程中会导致接收器信号的衰减,以及与频率相关的相位延迟,进而造成信号分散,最后导致符号间干扰(ISI),同时阻抗不连续导致的反射,也是导致符号间干扰的因素。

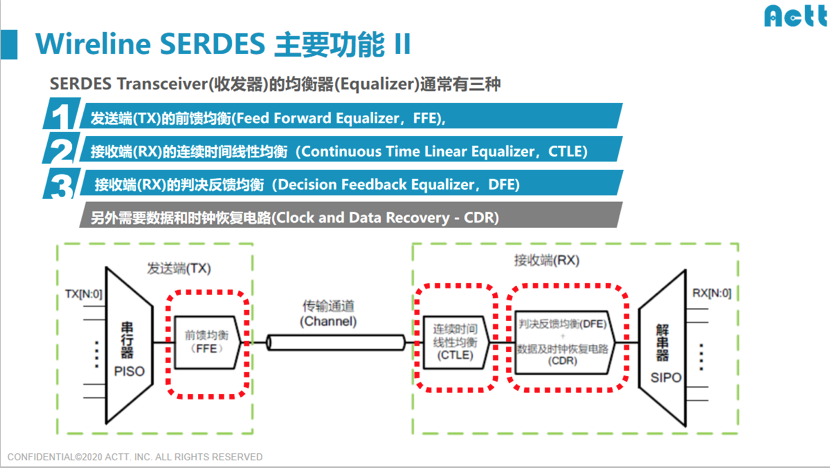

因此,ISI的设计关键,high speed Serdes需要做均衡。Serdes Transceiver(收发器)的均衡器通常有三种,包括发送端的前馈均衡, 接收端的连续时间线性均衡,接收端的判决反馈均衡,另外需要数据和时钟恢复电路。

均衡器在发送端或接收端,补偿信道的非理想性,消除码间干扰,从而使接收端的眼图重新张开。从时域上理解,均衡器是对脉冲响应信号重新塑形,把其能量限制在一个时间(1 UI)间隔之内,从而避免码间的干扰。

从频域上理解,均衡器是通过高通滤波器补偿信道的低通特性。

锐成芯微 SerDes 方案应用

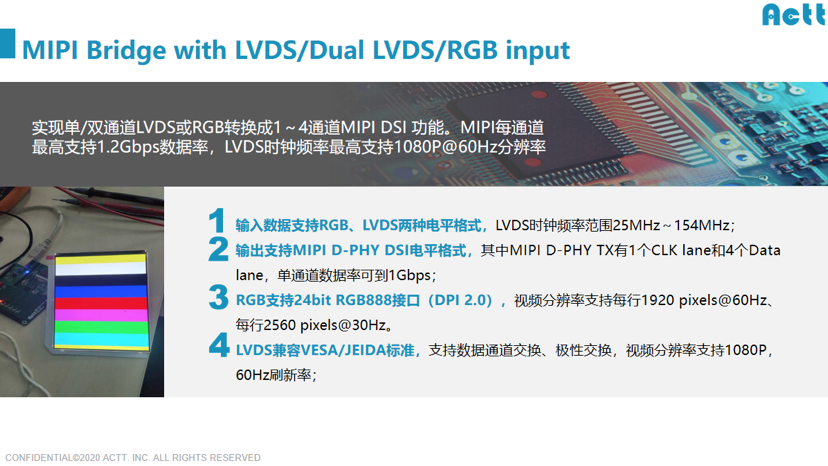

目前,成都锐成芯微 SerDes 方案涉及多个领域,包括SATA3.0、USB3.1 G1/G2、DDR3、DDR4、DP/HDMI及Ethernet IP等。除高性能CPU外,还可广泛应用于AI芯片,高速数据存储,高速音视频处理等领域。

(校对/kaka)

登录

登录