集微网消息(文/Kelven)7nm工艺的产品现在已经很成熟,基本踏进7nm的工艺时代,而PC市场Intel也终于要开始10nm工艺芯片的出货。工艺之争对于晶圆巨头来说,越来越激烈。

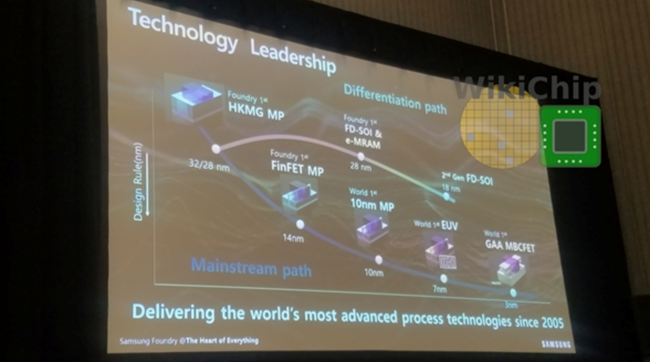

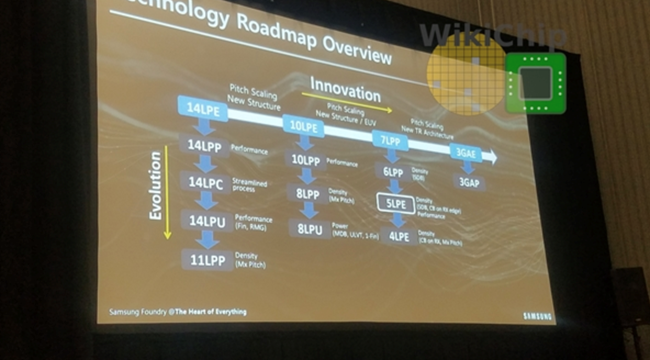

在三星日前的一场技术交流活动中,三星重新制订了未来的节点工艺细节。三星表示,EUV后,他们将在3nm节点首发GAA MCFET(多桥通道FET)工艺。由于FinFET的限制,预计在5nm节点之后会被取代。

对于三星来说,5nm工艺实际也只是7nm LPP的改良,可以被看作是第二代EUV。7nm LPP向后有三个迭代版本,分别是6nm LPP、5nm LPE和4nm LPE。

比较去年的泸县路,三星6LPP只是简单地引入SDB,从而提供了1.18倍的密度改进。另一个改变是删除4LPP节点,在路线图上只留下4LPE。三星将3 GAAE和3 GAAP更名为3 GAE和3 GAP。

根据理解,按照工艺核心指标,5nm LPE虽然沿用7nm LPP的晶体管和SRAM,但性能增强了11%,UHD下的密度会接近130 MTr/mm²,终于第一次超过了Intel 10nm和台积电7nm。(校对/慕容素娟)

登录

登录